#### It is the Instruction Fetch front-end

1

#### Stupid !!

#### André Seznec

#### Single thread performance

- Has been driving architecture till early 2000's

- And that was fun !!

- Pipeline

- Caches

- Branch prediction

- Superscalar execution

- Out-of-order execution

# Winter came on the architecture kingdom

3

- Beginning 2003:

- The terrible "multicore era"

- The tragic GPGPU era

- The Deep learning architecture

- The quantum architecture

#### The world was full of darkness

#### In those terrible days

- Parallelism zealots were everywhere.

- Even industry had abandoned the "Single Thread Architecture" believers

- Among those few:

- A group at INRIA/IRISA

#### But "Amdahl's Law is Forever"

5

• The universal parallel program did not appear

- Manycores are throughput oriented;

- The user wants short response time

Could it be that the old religion (single thread architecture) was not completely dead ?

#### And spring might come back

6

- Everyone is realizing that single thread performance is the key.

- Companies are looking for microarchitects:

- Intel, Amd, ARM, Apple, Microsoft, NVIDIA, Huawei, Ampere Computing, ..

- But a nightmare for publications:

- One microarchitecture session at Micro 2019

#### So we definitely need

7

#### A very wide-issue aggressively speculative supercalar core

#### Ultra High Performance Core (1)

- Very wide issue superscalar w oo engine! It's the stupid!!

- >= 8-wide

- Out-of-order

- 300-50

register file access ?

#### Ultra High Performance Core (2)

# Ultra High Performance Cor with use instruction Front-End ! It's the Instruction !!

s/memory dependencies ?

alues?

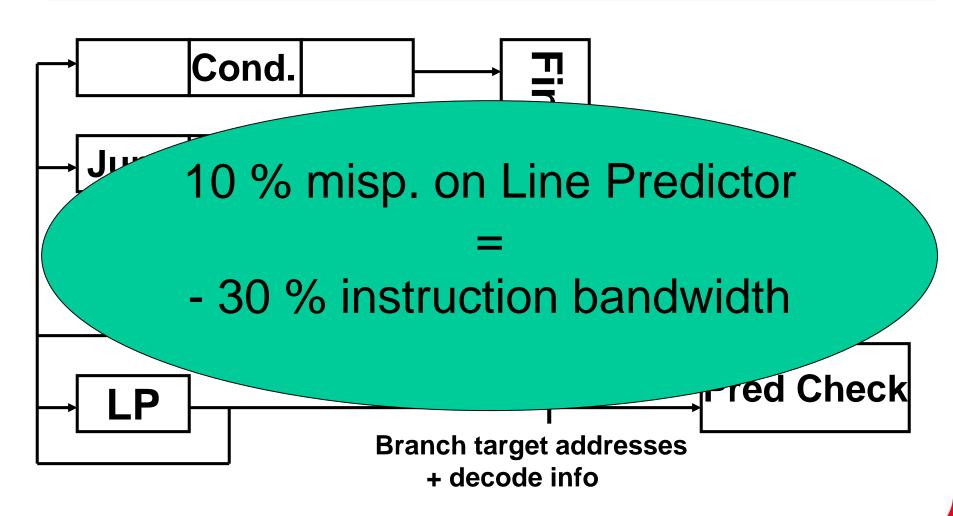

#### A block in the instruction front-end

- + memory dependency prediction

- + move elimination

- + value prediction (?)

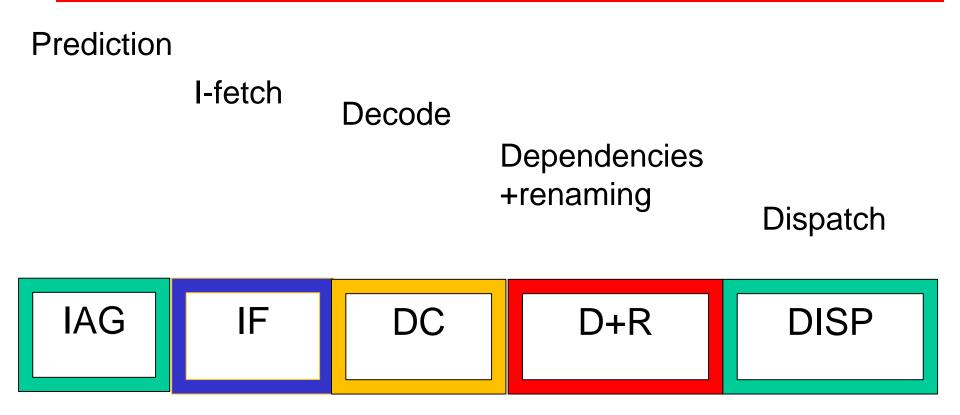

#### Instruction address generation

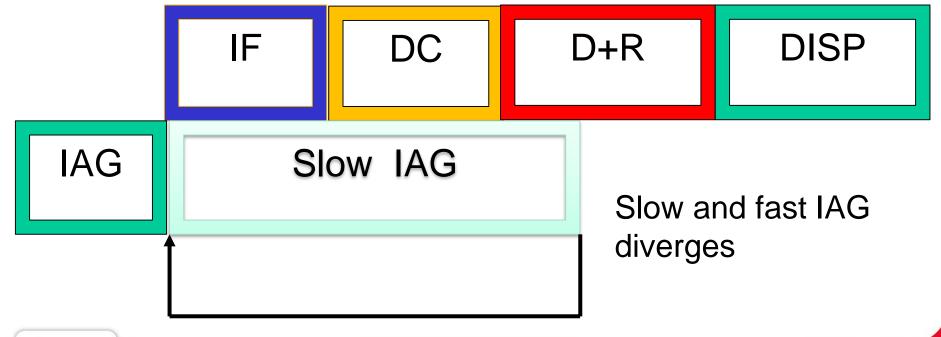

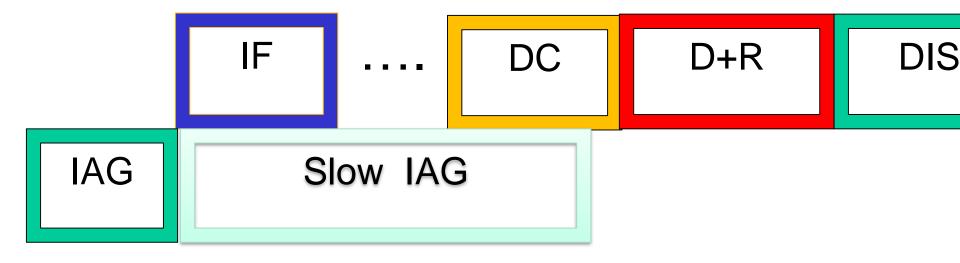

#### Hierarchical IAG (example)

- Fast IAG + Complex IAG

- Conventional IAG spans over <u>four cycles</u>:

- <u>3 cycles</u> for conditional branch prediction

- <u>3 cycles</u> for I-cache read and branch target computation

- Jump prediction, return stack read

- + 1 cycle for final address selection

- Fast IAG: Line prediction:

- a single 2Kentry table + 1-bit direction table

- select between fallthrough and line predictor read

nnía

Hierarchical IAG (2)

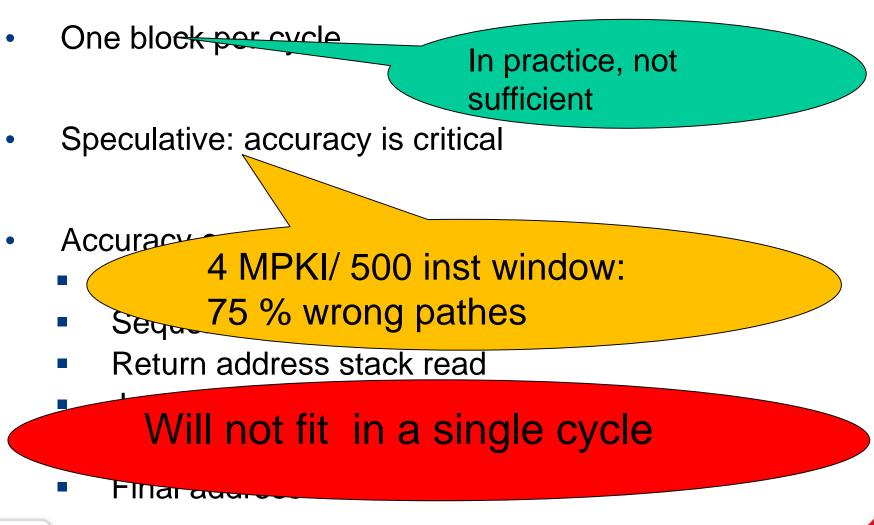

- You should fetch as much as possible:

- Contiguous blocks

- Across contiguous cache blocks !

- Bypassing not-taken branches !

- More than one block par cycle ?

Innía

#### Example: Alpha EV8 (1999)

- Fetches up to two, 8-instruction blocks per cycle from the I-cache:

- a block ends either on an aligned 8instruction end or on a taken control flow

- up to 16 conditional branches fetched and predicted per cycle

- Next two block addresses must be predicted in a single cycle

#### A block in the instruction front-end

#### If you overfetch ...

• Add buffers;

Ínría

Decode is not an issue

19

#### • If you are using a RISC ISA !!

#### • Just a nightmare on x86 !!

Innía

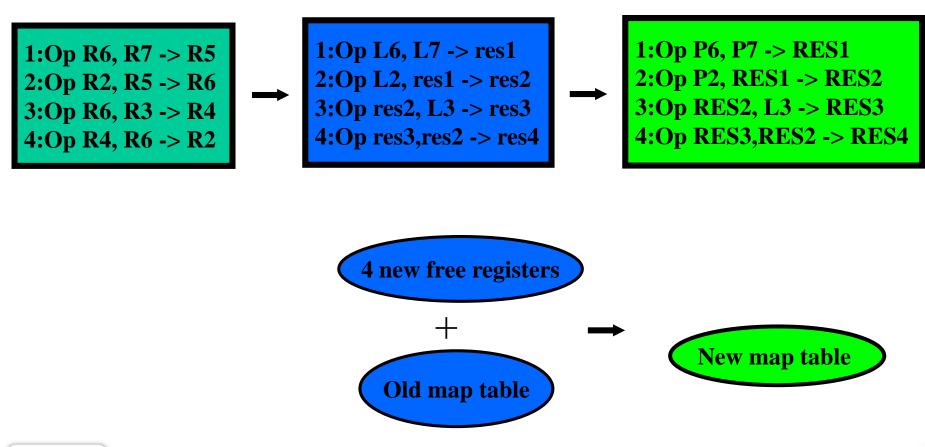

# Dependencies marking and register renaming

20

- Just need to rename 8 (or more) inst per cycle:

- Check/mark dependencies within the group

- Read old map table

- Get up to 8 free registers

- Update the map table

The good news: It can be pipelined

## Dependencies marking and register renaming (2)

#### OK, where are we?

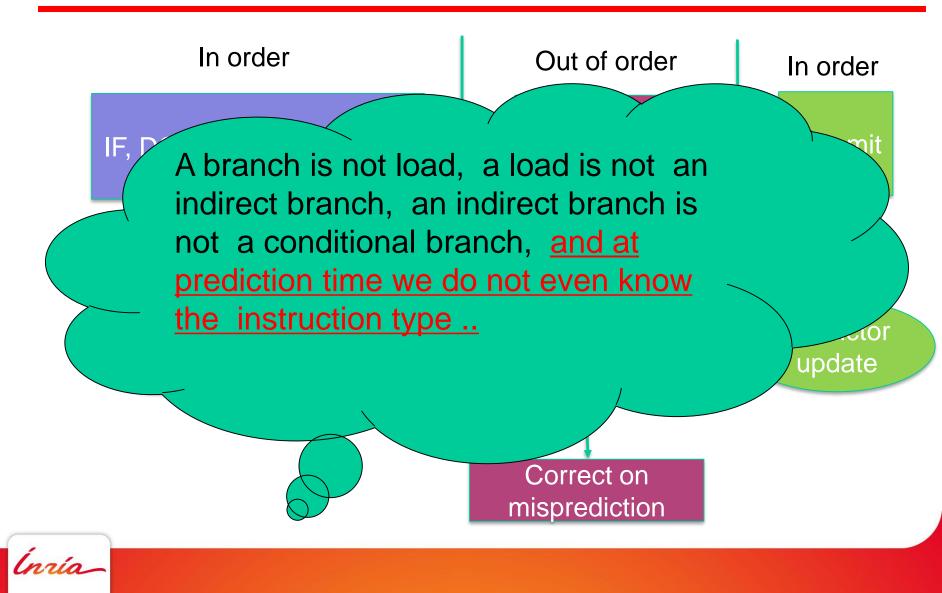

- Very long pipeline:

- ≈ 15-20 cycles before execution stage

- Misprediction is a disaster

- Very wide-issue

- Need to fetch/decode/rename  $\geq$  8 inst/cycles

- mis(Fast prediction) is an issue

- Misses on I-caches/BTB also a problem

#### Why branch prediction ?

• 10-30 % instructions are branches

• Fetch more than 8 instructions per cycle

- Direction and target known after cycle 20

- Not possible to lose those cycles on each branch

- PREDICT BRANCHES

- and verify later !!

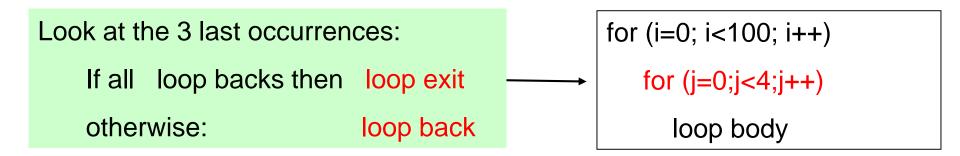

#### global branch history Yeh and Patt 91, Pan, So, Rameh 92

B1: if cond1

B2: if cond2

B3: if cond1 and cond2

B1 and B2 outputs determine B3 output

Innía

#### Exploiting local history Yeh and Patt 91

25

•A local history per branch

•Table of counters indexed with PC + local history

#### Speculative history must be managed <sup>26</sup> !?

- Local history:

- table of histories (unspeculatively updated)

- must maintain a speculative history per inflight branch:

- Associative search, etc ?!?

- Global history:

- Append a bit on a <u>single</u> history register

- Use of a circular buffer and just a pointer to speculatively manage the history

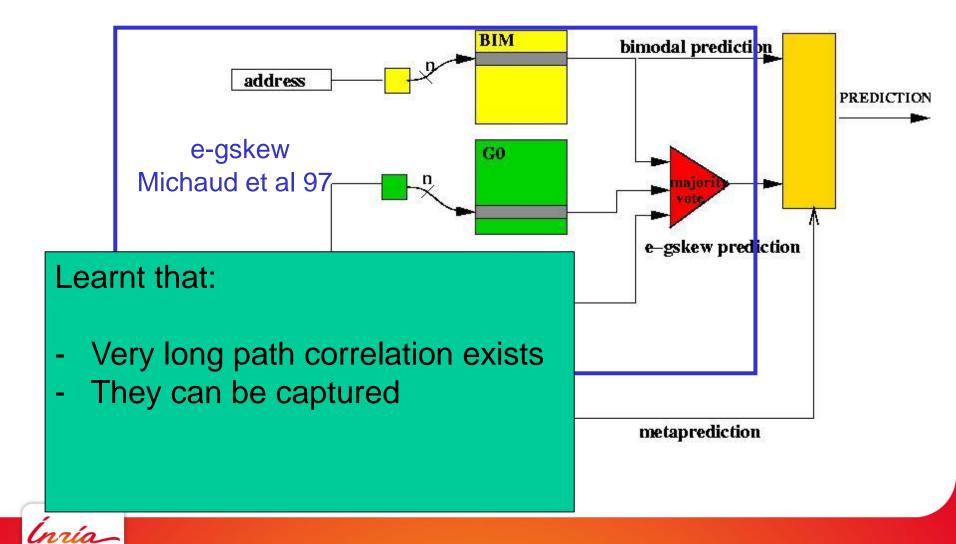

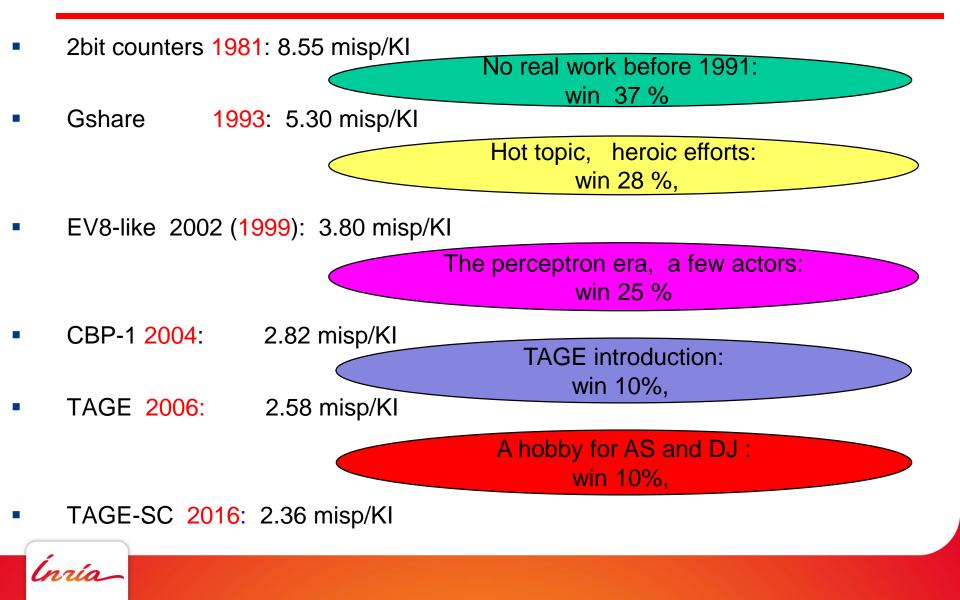

#### Branch prediction: Hot research topic in the late 90's

27

- McFarling 1993:

- Gshare (hashing PC and history) +Hybrid predictors

- « Dealiased » predictors: reducing table conflicts impact

- Bimode, e-gskew, Agree 1997

#### Essentially relied on 2-bit counters

#### EV8 predictor (1999): (*derived from*) 2bc-gskew

28

### In the new world

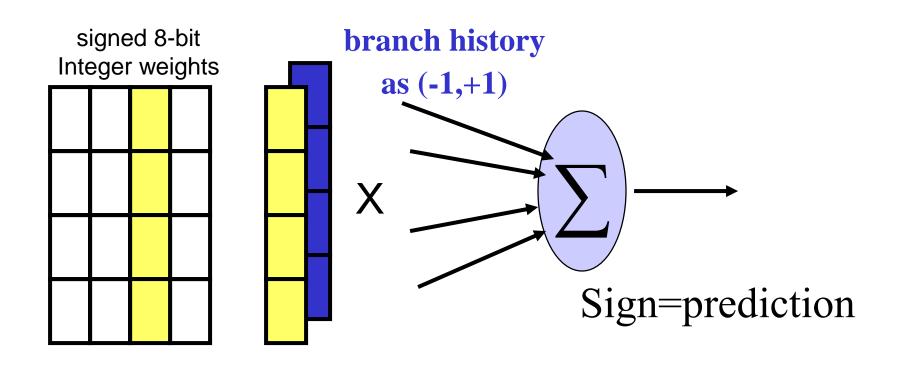

#### A UFO : The perceptron predictor Jiménez and Lin 2001

Update on mispredictions or if  $|SUM| < \theta$

#### (Initial) perceptron predictor

- Competitive accuracy

- High hardware complexity and latency

- Often better than classical predictors

- Intellectually challenging

Innía

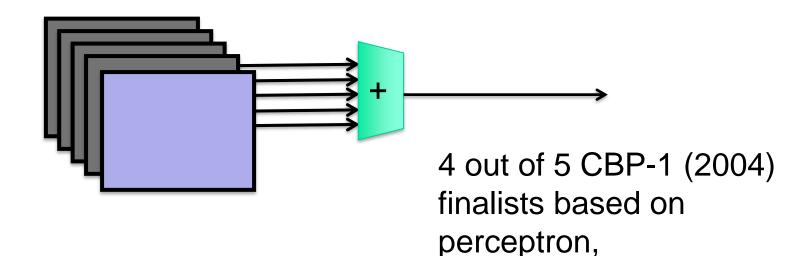

#### Rapidly evolved to

Can combine predictions: -global path/branch history -local history -multiple history lengths

#### An answer

• The geometric length predictors:

#### GEHL and TAGE

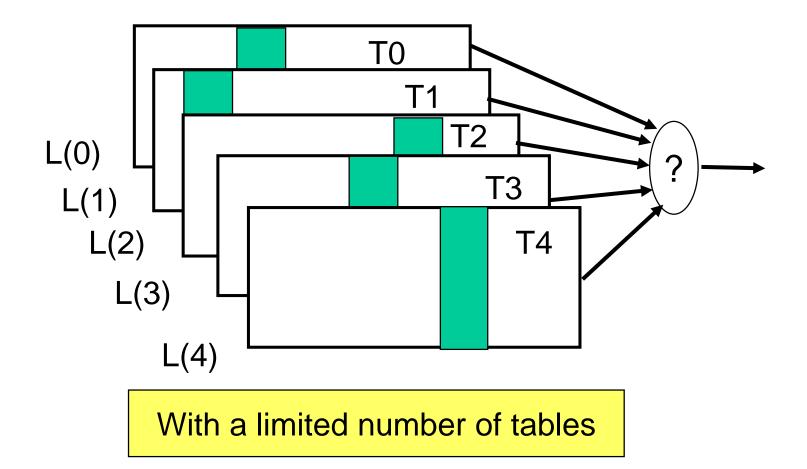

## The basis : A Multiple length global history predictor

- H and H' two history vectors equal on N bits, but differ on bit N+1

- e.g. L(1)≤N<L(2)

- Branches (A,H) and (A,H') biased in opposite directions

Table T2 <u>should allow</u> to discriminate between (A,H) and (A,H')

#### GEometric History Length predictor

The set of history lengths forms a geometric series

$$L(0) = 0$$

$$L(i) = \partial^{i-1}L(1)$$

{0, 2, 4, 8, 16, 32, 64, 128}

What is important: L(i)-L(i-1) is drastically increasing

Spends most of the storage for short history !!

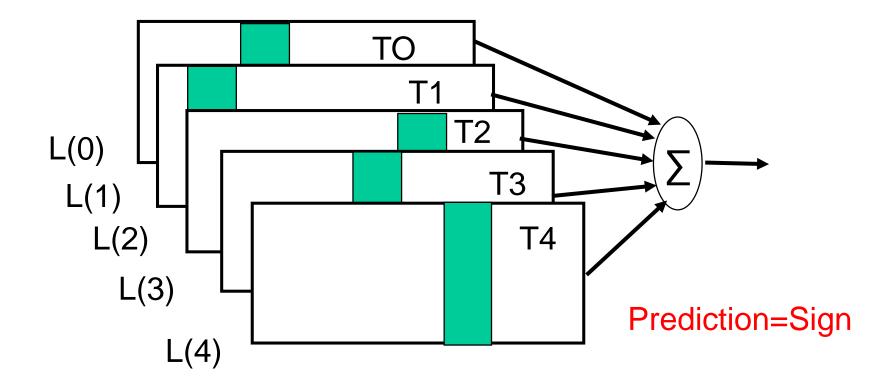

# GEHL (2004) prediction through an adder tree

Using the perceptron idea with geometric histories

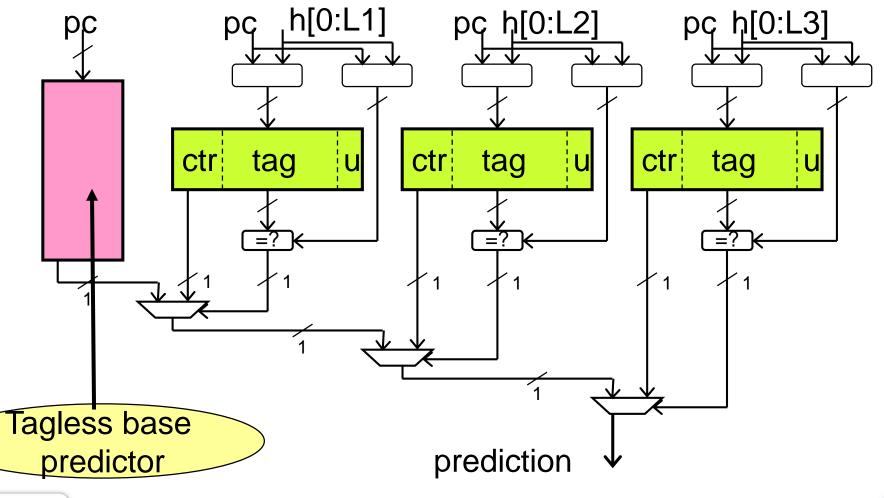

## TAGE (2006) prediction through partial match

Ínría

## The Geometric History Length Predictors

39

- Tree adder:

- O-GEHL: Optimized GEometric History Length predictor

- CBP-1, 2004, best practice award

- Partial match:

- TAGE: TAgged GEometric history length predictor

- + geometric length

- + optimized update policy

- Basis of the CBP-2,-3,-4,-5 winners

- Inspiration for many (most) current effective designs

### A BP research summary (CBP1 traces)

And indirect jumps?

## TAGE principles to indirect jumps:

"A case for (partially) tagged branch predictors", JILP Feb. 2006

The 3 first ranked predictors at 3<sup>rd</sup> CBP in 2011 were ITTAGE predictors

## Memory (in)dependencies predictors

42

To allow load and stores to execute out-of-order

- Naive: dependent/independent

- Wait: e.g. Store sets

- Store forwarding: bypass the cache

- Register producer to consumer forwarding

## A speculation opportunity on RISC ISA

The Omnipredictor (PACT 2018)

Consolidating several types of speculation in a single predictor structure : TAGE.

Memory dependency prediction and indirect target prediction through TAGE and the BTB at zero storage overhead.

•Omnipredictor: a good fit for mid-range cores with constrained hardware budget

#### Value Prediction ?

• Also in the front-end ..

- Predictions should be done in the front-end

- Control-flow could be used to predict

- Values

- Value equality

- Register equality

#### **Issues in Front-End**

High instruction footprint applications (servers, cloud, web browsers, ..)

- Instruction cache misses

- BTB misses

Innia

#### Summary

47

- Single thread performance was, is and will be a major issue:

- Industry is eager to deliver, but limited progress

• More « a la grand papa » microarchitects needed

#### A few relevant publications

- A. Seznec, S. Felix, V. Krishnan, Y. Sazeides, "<u>Design trade-offs on the</u> <u>EV8 branch predictor</u>", ISCA 2002

- A. Seznec, P. Michaud, <u>"A case for (partially) tagged Geometric</u> <u>History Length Branch Prediction</u>", JILP, Feb. 2006,

- A. Perais , A. Seznec. <u>Practical Data Value Speculation for Future High-</u> end Processors. HPCA 2014

- A. Perais, F.A. Endo, A.Seznec. Register Sharing for Equality Prediction. Micro 2016,

- A. Perais, A. Seznec, <u>Cost Effective Speculation with the Omnipredictor</u> PACT '18

nnia