# October FOLD RAISC-V 2nd Week in Paris only

#### Silicon At The Speed Of Software

# OR RISC-V

d week

SiFive's founders are the same UC Berkeley professor and PhDs who invented and have been leading the commercial implementation of the RISC-V Instruction Set Architecture (ISA) since 2010

**Si**Five

# SiFive in a nutshell

### Massive Growth in Devices & Data

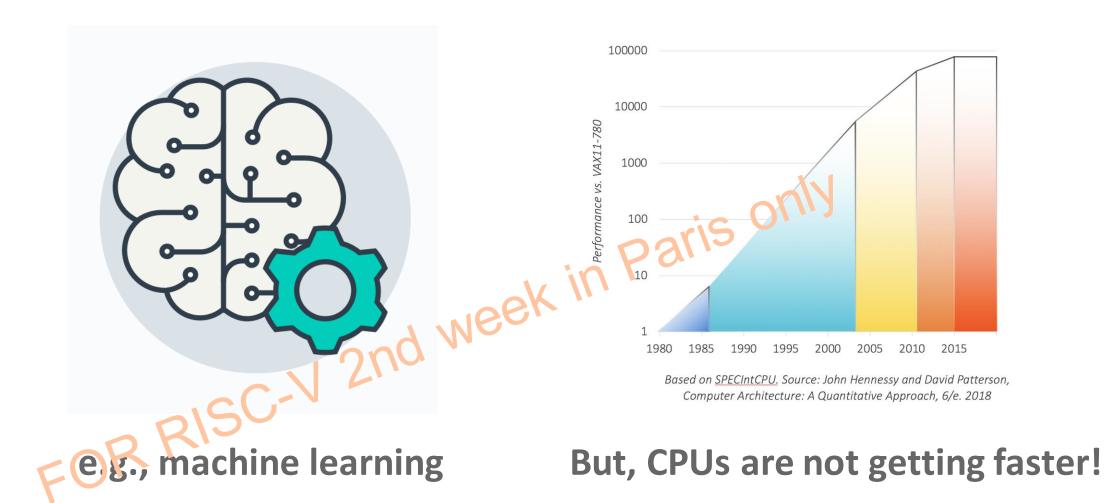

### **Compute Needs Are Changing**

Source: Medium, Entering the world of Machine Learning

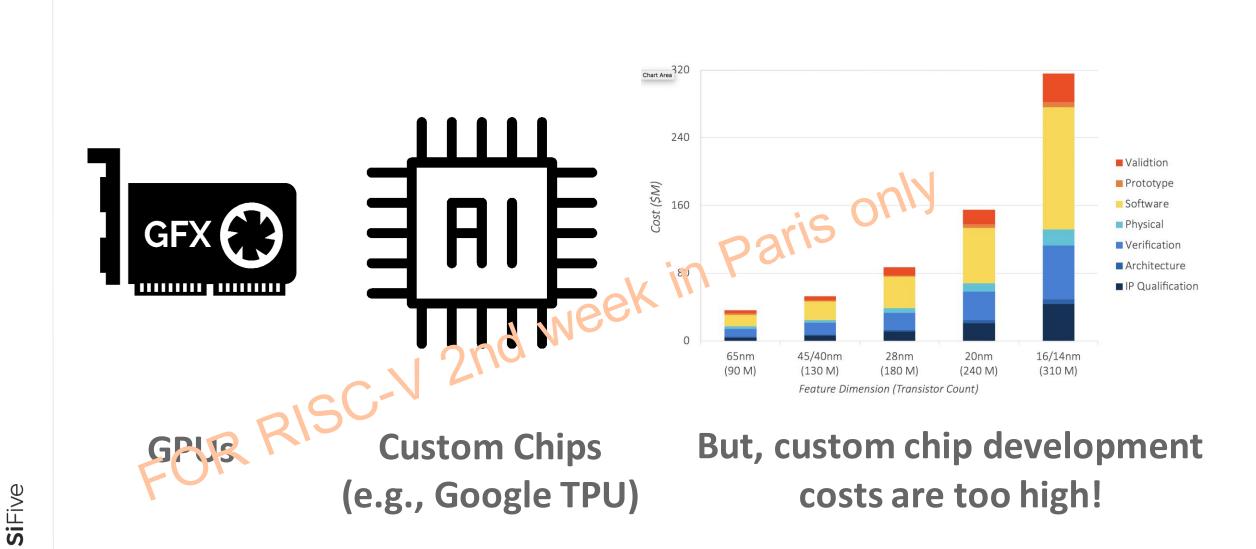

# Hardware Trends: Custom Hardware To The Rescue!

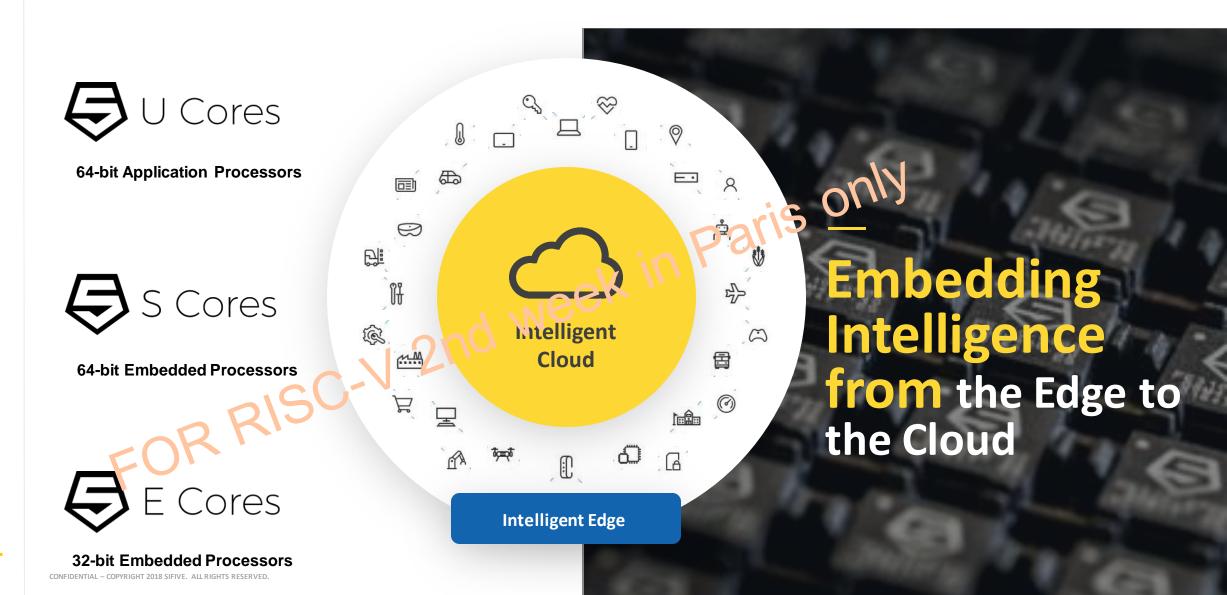

# **Embedding Intelligence: From the Edge to the Cloud**

**Si**Five

# SiFive Core IP RISC-V Configurable Cores

|                                                               | ECores 32-bit embedded cores<br>MCU, edge computing,<br>AI, IoT                          | <b>SCores</b><br><b>64-bit embedded cores</b><br>Storage, AR/VR, machine<br>learning | <b>UCORES</b><br><b>64-bit application cores</b><br>Linux, datacenter, network<br>baseband                          |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 7 Series                                                      | E7 Series                                                                                | S7 Series                                                                            | U7 Series                                                                                                           |

| <b>Highest</b><br>performance:<br>8-stage, dual-issue         | <b>&gt; E76-MC</b> Compare to Cortex-M7 Quad-core 32-bit embedded processor              | <b>S76-MC</b> No 64-bit Cortex equivalent Quad-core 64-bit embedded processor        | <b>&gt; U74-MC</b> Compare to Cortex-A55 MP4<br>Multicole four U74 cores and one S76 core                           |

| superscalar pipeline                                          | > E76 Compare to Cortex-M7<br>High performance 32-bit embedded core                      | <b>S76</b> No 64-bit Cortex equivalent<br>High-performance 64-bit embedded to re     | > Compare to Cortex-A55<br>High performance LInux-capable processor                                                 |

| 3/5 Series                                                    | E3 Series                                                                                | S5 Series                                                                            | U5 Series                                                                                                           |

| <b>Efficient</b><br><b>performance:</b><br>5–6-stage, single- | <b>&gt; E34</b> Compare to Cortex-R5F.<br>E31 features + single-precision floating point | S51 features + single-precision floating point                                       | <b>&gt; U54-MC</b> Compare to Cortex-A53<br>Multicore application processor with four U54<br>cores and one S76 core |

| issue pipeline                                                | > E31 Compare to Cortex-R5<br>Balanced porformance and efficiency                        | > S51 No 64-bit Cortex equivalent<br>Low-power 64-bit MCU core                       | <b>&gt; U54</b> Compare to Cortex-A53<br>Linux-capable application processor                                        |

| 2 Series                                                      | CE2 Series                                                                               | S2 Series                                                                            |                                                                                                                     |

| Power & are a<br>o timi. ed:<br>2- 3-stage, single-           | <b>E24</b> Compare to Cortex-M4F E21 + single-precision floating point                   | > S21 No 64-bit Cortex equivalent<br>Area-efficient 64-bit MCU core                  |                                                                                                                     |

| issue pipeline                                                | E21 Compare to Cortex-M4<br>E20 + User Mode, Atomics, Multiply, TIM                      |                                                                                      |                                                                                                                     |

| A.                                                            | > E20 Compare to Cortex-M0+<br>Our smallest, most efficient core                         |                                                                                      |                                                                                                                     |

8

CONFIDEN

# **SiFive Cloud Services**

- SiFive Core Designer

- Click to configure a RISC-V Core!

- RTL download in 24hrs!

- Core IP configured to your needs!

| SiFive Core Designer                                                                                                             |  | U7 Series                                                                                                                             |                                                                                       |                                                                                                                           |                                                                          | Review                                                                                                      |   |

|----------------------------------------------------------------------------------------------------------------------------------|--|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---|

| <ul> <li>Click to configure a RISC-V Core!</li> <li>RTL download in 24hrs!</li> <li>Core IP configured to your needs!</li> </ul> |  | Modes & ISA<br>On-Chip Memory<br>Ports<br>Security<br>Debug<br>Interrupts<br>Design For Test<br>Power Management<br>Branch Prediction | Modes & ISA                                                                           | U7 Series Core Complex<br>U7 SERIES CORE 10                                                                               | Front Port<br>64-bit AXI4<br>System Port<br>64-bit AXI4 →                |                                                                                                             |   |

|                                                                                                                                  |  |                                                                                                                                       | Number of Cores                                                                       | Machine Mode - User Mode<br>Multiply - Atomics - FP (F & D)<br>No SCIE - O Local Interrupts                               |                                                                          |                                                                                                             |   |

|                                                                                                                                  |  |                                                                                                                                       |                                                                                       | Perf. Optimized Brand<br>Clock Gating<br>Instruc. Cache<br>32 KiB - 8-way<br>Instruc. TIM<br>None<br>No Instruction Trace | PMP 8 Regions<br>Data Cache<br>32 KiB + 8-way<br>Data Loc. Store<br>None | Peripheral Port<br>64-bit AXI4 →<br>Memory Port<br>128-bit AXI4 →<br>L2 Cache<br>128 KiB<br>8-way<br>1 Bank | + |

|                                                                                                                                  |  |                                                                                                                                       |                                                                                       | Debug Module<br>JTAG • SBA<br>2 HW Breakpoints<br>0 Ext Triggers<br>Base: U74 Standard Core I2                            | PLIC<br>7 Priority Levels<br>127 Global Int.                             | CLINT                                                                                                       |   |

|                                                                                                                                  |  |                                                                                                                                       | Extensions          SiFive Custom Instruction Extension (SCIE)         On-Chip Memory |                                                                                                                           |                                                                          |                                                                                                             |   |

|                                                                                                                                  |  |                                                                                                                                       |                                                                                       |                                                                                                                           |                                                                          |                                                                                                             |   |

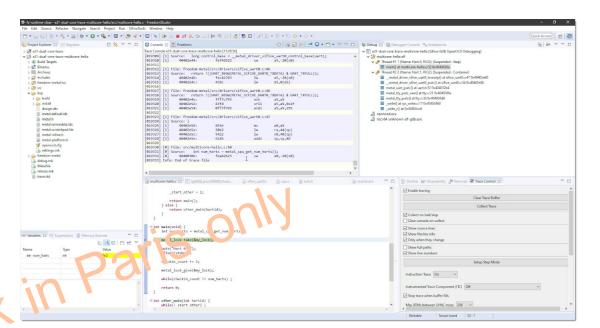

# **Quarterly updates**

- SiFive delivers IP and product updates on a quarterly basis

- Q3 Update includes Nexus 5001 trace encoders

- SiFive Freedom Studio support

- Open Source RISC-V Trace Decoder now on github

FOR RISC-V 2nd Week

SiFive Freedom Studio

SiFive

# Learn More - SIFIVE.COM

- HiFive Unleashed

- Quad Core Linux Capable CPU

- Available via CrowdSupply

- SiFive World Tour

- 50-City Tour

- SiFiveTechSymposium.com

FOR RISC-V 2nd

Sir

ashed

#### **SiFive Commercial Success**

**Si**Five

13

#### **SoC** security best practices

# **RISC-V SoC needs more security**

SiFive

### Silicon At The Speed Of Software

and updates on SiFive architectures!

Linley Fall Processor Conference 2019

Santa Clara, CA., USA October 23<sup>rd</sup> & 24<sup>th</sup>