# Enhanced Tools for RISC-V Processor Development and Customization

Zdeněk Přikryl (prikryl@codasip.com)

Chris Jones (jones@codasip.com)

# Who is Codasip?

- The leading provider of RISC-V processor IP

- Company founded in 2014 in the Czech Republic

- Founding member of the RISC-V Foundation, <u>www.riscv.org</u>

- Member of several working groups in the Foundation

- Actively contributing to LLVM and other open-source projects

- Now Codasip GmbH

- Headquarters in Munich, Germany

- R&D in Brno, Czech Republic

- Offices in Silicon Valley, US, and Shanghai, Pudong PRC

# Codasip Solutions

- Codasip Bk = portfolio of RISC-V processors

- Codasip Studio = unique design automation toolset for easy processor modification

- Performance/power efficiency and low-cost

- Algorithm acceleration (DSP, security, audio, video, etc.)

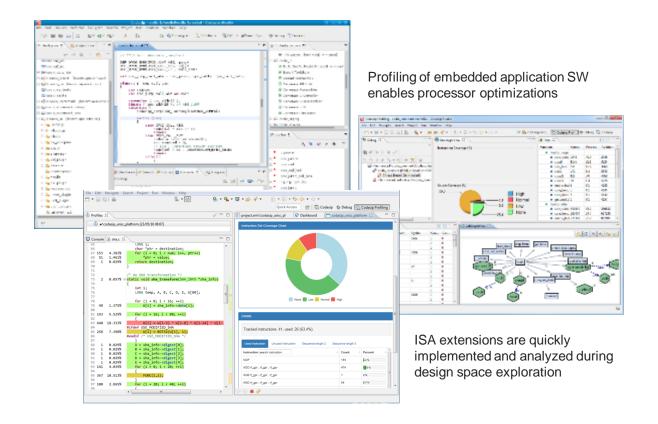

- Profiling tools of embedded SW for tailoring processor IP

- CodAL = Codasip's own proprietary C-like language for processor architecture description

Codasip introduced its first RISC-V processor in November 2015

### Bk: Customizable RISC-V Cores

**Bk** = the Berkelium series, Codasip's RISC-V processors

- Available immediately

- Pre-verified, tape-out quality IP

- Users do not need to verify IP

- ✓ Industry-standard interfaces

- AMBA for instruction and data bus

- JTAG (4pin/2pin) for debugging

### Fully customizable

- Support for all RISC-V ISA standard extensions

- Enable easy creation of performance-enhancing resources, such as:

- Custom registers for computations

- Custom control-status registers

- Novel interfaces such as GPIO, FIFO, scratch-pad memory

- Even pipeline modifications are possible

- Bk core CodAL source as the starting point for your own RISC-V core

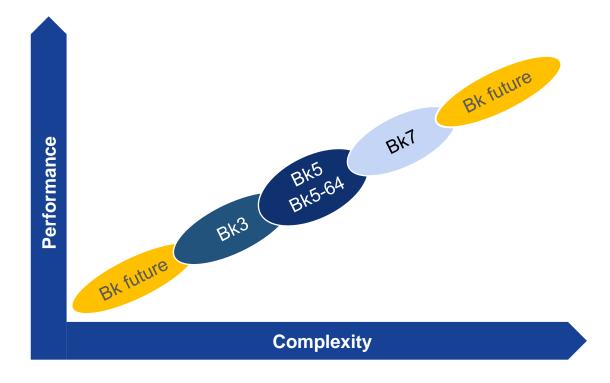

## **Bk Cores Roadmap**

Comprehensive offering including new advanced designs

#### Bk3

Entry-level 32bit RISC-V core

### Bk5, Bk5-64

32bit and 64bit RISC-V cores with balanced pipeline

#### Bk7

Linux-ready 64bit RISC-V core

#### **Future Bk**

- High-performance RISC-V cores

- Advanced pipeline

- Advanced DSP features

- Energy-efficient/low power RISC-V cores

#### All Bks

- Rich set of configuration options

- Fully customizable

### Standard and Custom Extensions

RISC-V offers a wide range of ISA modules:

- I/E for integer instructions

- M for multiplication and division

- **C** for compact instruction

- F/D for floating point operations

- WIP: **B**, **P**, **V**, ...

However, it may **not be enough** for your application domain or if you are looking for a key **differentiator...**

# Why Customized Tools?

One of the biggest advantages of the RISC-V open ISA is **customization**. However, a customized processor also needs a customized SDK...

# Standard customization (manually adding custom ISA extensions):

- 1. Model and simulate a new instruction

- 2. Modify the compiler

- 3. Modify assembler

- 4. Add support in the debugger

- 5. Verify, verify, verify...

- → Challenging, time-consuming, expensive

# Benefits of automatic generation of customized tools:

- Reduced time needed for tool modification

- Reduced cost of custom processor development

- ✓ The resultant processor is easily programmable using standard C/C++

- Proven open-source technologies and frameworks allow for easy integration

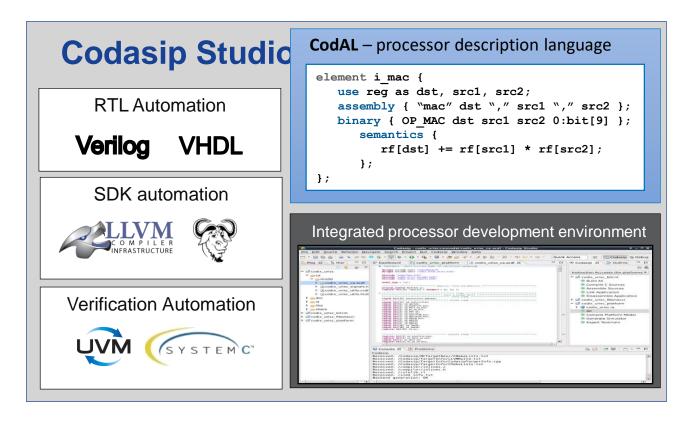

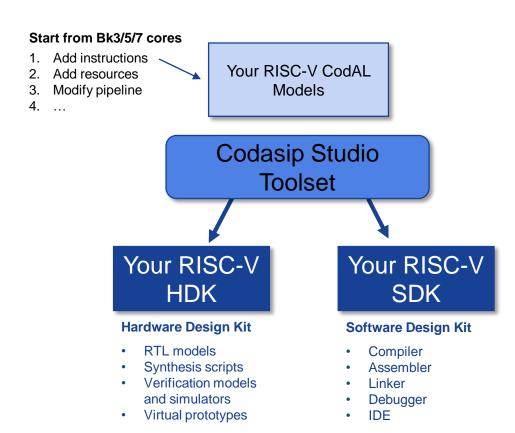

## What is Codasip Studio?

A unique collection of tools for **fast & easy modification** of RISC-V processors. **All-in-one**, highly automated. Introduced in 2014, **silicon-proven** by major vendors.

#### Customization of base instruction set:

- Single-cycle MAC

- Custom crypto functions

- And many more...

### Complete IP package on output:

- C/C++ LLVM-based compiler

- C/C++ Libraries

- Assembler, disassembler, linker

- ISS (incl. cycle accurate), debugger, profiler

- UVM SystemVerilog testbench

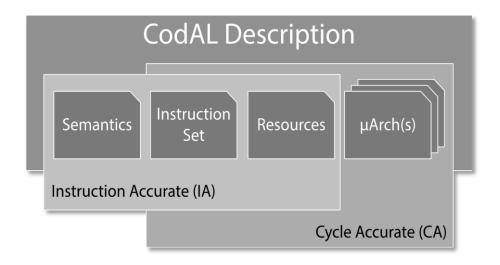

### CodAL Models

- Easy-to-understand C-like language that models a rich set of processor capabilities

- All Codasip processors are created and verified using CodAL

- Multiple microarchitectures can be implemented in a single CodAL model

- CodAL models are provided to Codasip IP customers as a starting point for their own processor optimizations and modifications

### Example: B Extension Functional Model

- Written in CodAL

- in 10 days by a single engineer

- 900 lines of code

- Software development kit (SDK) automatically generated by Studio, including

- Instruction set simulator (ISS)

- Profiler to check the impact of the extensions

- C compiler

- Able to use a subset of instructions automatically (rotations, compact instructions, shifts, etc.)

```

element i_gzip

{

use opc_gzip as opc;

use reg_any as dst, src1;

use shift_imm as imm;

assembler { opc dst "," src1 "," imm};

binary { opc[OPC_FRAG_SHIFT] imm src1 opc[OPC_FRAG1] dst opc[OPC_FRAG0] };

semantics

{

rf_gpr_write (dst, gzip_uXlen(rf_gpr_read(src1), imm));

};

};

set isa_b += i_gzip;

```

## Example: B Extension Implementation Model

- Written in CodAL

- in 3 weeks by a single engineer

- 1500 lines of code

- Hardware design kit (HDK) automatically generated by Studio, including

- RTL

- Testbench

- UVM-based verification environment

```

#ifdef OPTION_EXTENSION_B

case SLO:

ex result = ones shifter 32(5LO, ex aluop1, ex aluop2);

case SRO:

ex_result = ones_shifter_32(SRO, ex_aluop1, ex_aluop2);

break;

case ANDC:

ex result = (uXlen)ex aluop1 & (~ ex aluop2);

case ROTR :

ex result = ex aluop1 >>> ex aluop2;

break;

case ROTL :

ex_result = ex_aluop1 <<< ex_aluop2;

break;

case CTZ:

ex_result = codasip_ctlz_uint32(ex_aluop1);

break;

case CLZ :

ex result = codasip cttz uint32(ex aluop1);

break;

#endif

```

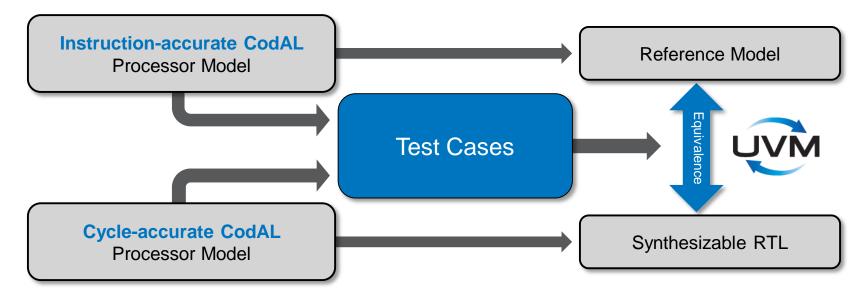

### Processor IP Verification

- Strong methodology based on standardized approach, simulation, and static formal analysis

- Consistency checker

- Random assembler program generator

- UVM verification environment

- Environment in SystemVerilog generated automatically by Codasip Studio

- Checking if RTL corresponds to specification

Codasip GmbH

13

## **Bk Core Customization with Codasip Studio**

# Summary

# 1. Codasip is the leading provider of commercial-quality RISC-V IP

- Comprehensive off-the-shelf portfolio

- From 32bit embedded to 64bit Linuxready cores

- Complete, fully verified IP packages

- Available immediately

- Full-time, highly professional customer support staff

# 2. Codasip offers easy, automatized way to customize RISC-V

- Customization brings more performance, lower power/area, and differentiation

- Codasip provides a complete set of tools and resources to customize:

- CodAL C-like language for processor description

- Codasip Studio a complete customization toolset

## Thank you!

Questions?