# Development of an RV64GC IP core for the GRLIB IP Library

Johan Klockars Cobham Gaisler info@gaisler.com

## Background

### Cobham Gaisler AB

#### Since 2 December 2014

- **Cobham Gaisler** is a world leader in processors for space applications like satellites & launchers

- Located in Gothenburg, Sweden

- Established in 2001 and acquired by Aeroflex in 2008

- Fully owned subsidiary of Cobham plc since 2014

- Management team with >100 years combined experience in the space sector:

- 34 employees with expertise within electronics, ASIC and software design

- Complete facilities in-house for ASIC and FPGA design

- Cobham has 15+ years experience designing open hardware

- RISC-V Foundation member 2019

To provide processors that enable new scientific missions, and allow new ways to utilize space constellations for commercial use.

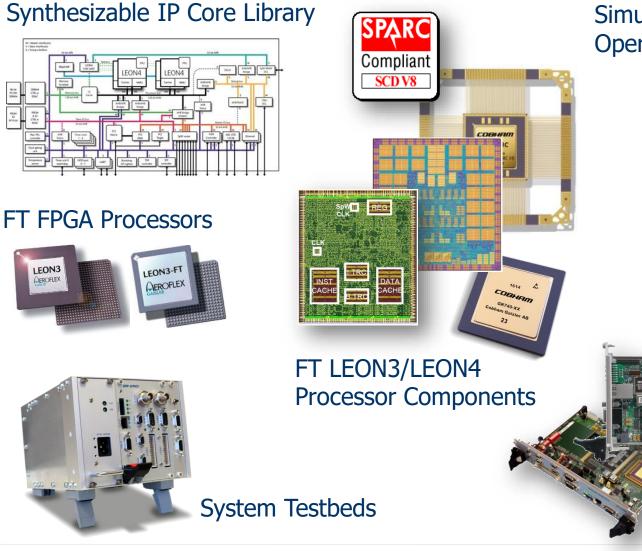

### **Cobham Gaisler Processor Solutions**

One-Stop-Shop

#### Simulators, Debuggers, Operating Systems, Compilers

Development Boards

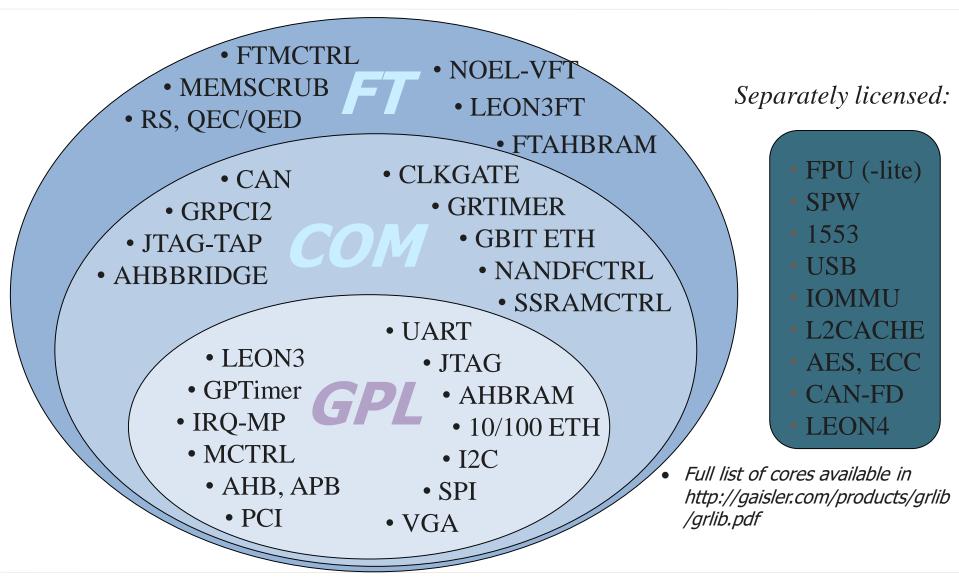

### GRLIB Distributions: GPL, Commercial, Fault-Tolerant

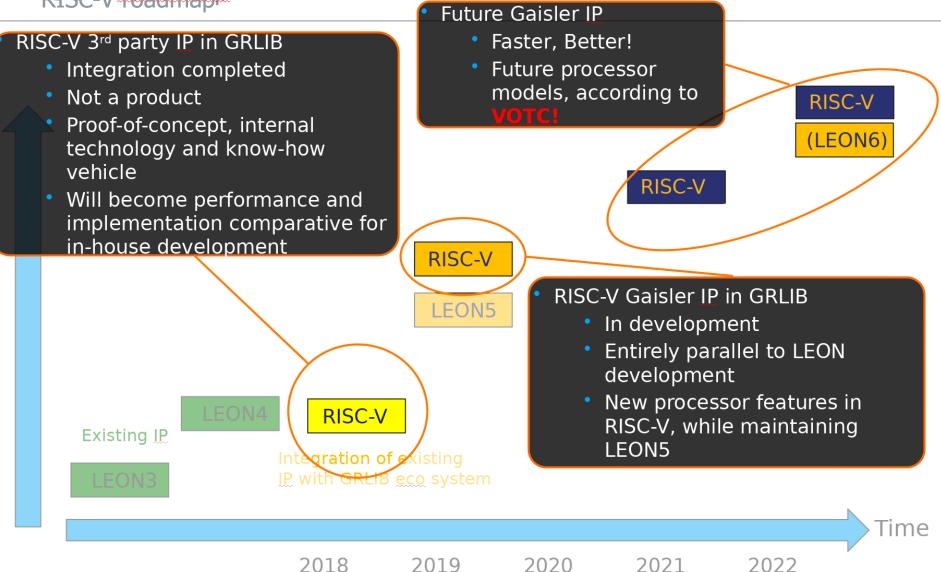

### **Cobham is now a Multi-Architectural Company**

Cobham continues to be committed to and invested in the SPARC architecture and its LEON implementations.

SPARC/LEON <u>will be maintained and further</u> <u>developed</u> going forward. The company has customers expecting it to provide components and support for decades to come. This is also ensured via long term supply agreements.

The RISC-V architecture is expected to grow in the future with a larger number of developers compared to SPARC V8.

Going forward, Cobham will add RISC-V to its product portfolio <u>as a complement</u> to SPARC and ARM, <u>not as a replacement</u>.

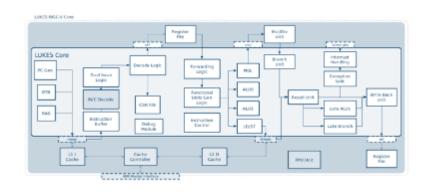

# What is NOEL-V?

### **NOEL-V Processor Core**

#### **Primary goals:**

- RISC-V 64-bit compliant processor core

- Fault Tolerance Error Correction Codes (ECC)

- Cybersecurity (proprietary solutions)

- Enable ISO 26262/FUSA certification (Road vehicles – Functional safety)

- Leverage foreseen uptake of RISC-V software and tool support in the commercial domain

- Compatible with GRLIB IP Core library

#### **Target applications:**

- General purpose payload processing

- Mixed platform and payload applications

- With future DDR4 SDRAM controller, specifically targeted for space applications

#### **Target technologies:**

- ASIC implementations for space applications

- High-end space FPGAs: Kintex Ultrascale

### **NOEL-V Features**

### • RISC-V RV64GCN

- M mul/div

- F 32 bit float

- C 16 bit instructions

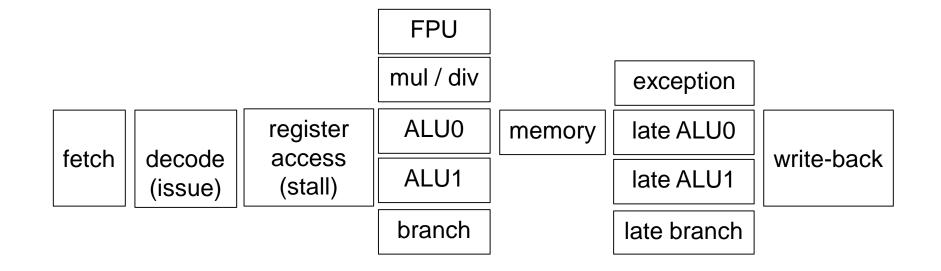

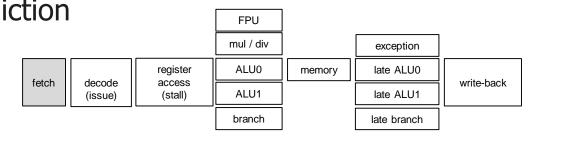

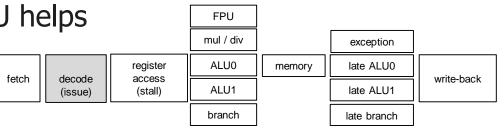

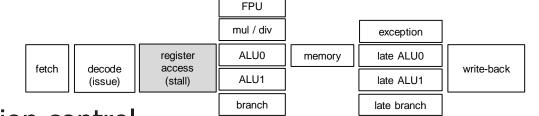

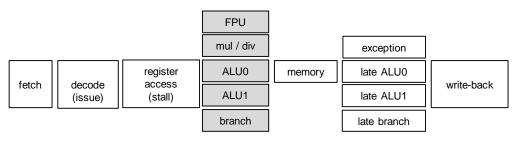

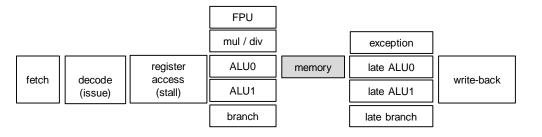

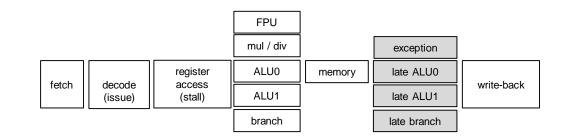

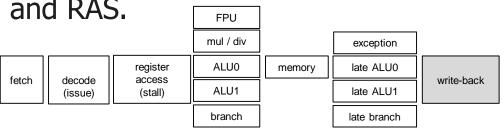

- 7-stage dual-issue in-order

- Late ALUs and branch unit

- M/S/U with MMU

- SMP/AMP hardware coherency

- RISC-V PLIC

- Multi-core

- A atomics

- D 64 bit float

- N user-level interrupts

- Dynamic branch prediction

- Blocking write-through L1

- PMP

- Hypervisor (pending standardization)

- RISC-V debug specification

- AMBA 2.0 AHB (subsystems with L2 cache and AXI4)

### Fault tolerance

- For space, fault tolerance is necessary.

- Various choices regarding ECC, parity etc.

- What to do when non-correctable RAM errors are detected?

- Requirement:

- Deterministic and safe behavior.

- Wish:

- Be able to log the fault, on best-effort-basis, to external storage.

- RISC-V leaves CPU response on HW fault to the implementation

- no dedicated exception number assigned for bus access fault, IU register error, FPU register error, etc.

- no semantic on CPU response to the above events

- mtval may not be enough (SW-writable, nesting faults?)

- NOEL-V approach to be determined.

### Combined processor roadmap

RISC-V-roadmap-

### **NOEL-V** Performance

- No work on compiler/libraries for NOEL-V yet.

- Testing on Kintex Ultrascale (KCU105) at 100 MHz.

- LEON5 has been measured at (Cobham gcc):

- 3.14 DMIPS/MHz

(-O3 and all files are combined during compilation)

- 4.57 Coremark/MHz

(-O3 -mcpu=leon5 -msoft-float -DPERFORMANCE\_RUN=1 -funroll-all-loops -finline-functions -finline-limit=1000)

- Very preliminary, NOEL-V simulated (standard toolchain)

- 4.36 CoreMark/MHz (ee\_u32 as signed)

### **NOEL-V Relation to LEON5**

- Related micro-architectures, but separate teams.

- NOEL-V development started later, so reuse.

- Partial reuse

- Principles of the integer pipeline

- Similar branch prediction

- Complete (more or less) reuse

- FPU

- Instruction and data cache

- MMU and cache controller

### **NOEL-V Synthesis configurability**

### Planned

- MCADFN

- Virtual address space

- Late ALU

- Caches

- TLB

- Branch prediction

### **Possibilities for later**

- 32 bit

- Non-standard instructions

- U/S (MMU)

- Physical address space

- Late branch

- FPU

- PMP

- Single-issue

• B / P / V • ....

# For who is NOEL-V?

### Why another RISC-V implementation?

- Cobham is developing its own RISC-V implementation:

- As opposed to licensing from 3<sup>rd</sup> party

- Full control of the design means short path to new custom features

-I.e. not dependent on external IP

- Experienced processor team in-house

- GRLIB based implementation existing infrastructure

- Allows for flexible license options

- Flight

- Commercial

- Educational

- Hobbyist

### Licensing model

- Parts of GRLIB are under an open license

- The intention is to do the same with NOEL-V

- GPL, CC, CERN OHW, solderpad,...

- Any user can evaluate on FPGA development board

- Academic use without complicated license setup

- Hobbyists

- Fault-tolerant functionality in the flight license

- Netlist, encrypted RTL

- NOEL-V will be distributed from Q1 2020

## Development

# COBHAM

- Not Chisel, SpinalHDL, Lava, MyHDL, Migen,...

- Few developers familiar with them

- HW engineers often not computer scientists

- No support from tool vendors

- Not HLS

- Mostly as above

- Questionable performance

### VHDL

- Really nice, when used "the right way"

- Very common, in Europe at least

- We can find developers

- Our users can understand

- Well established among customers in the space domain

- Good tool support

- Including free simulator

- Logical equivalence checkers

- GRLIB and LEON3-5

- "Classic" VHDL, to maximize tool support

- Strive for code clarity, and rely on the tools!

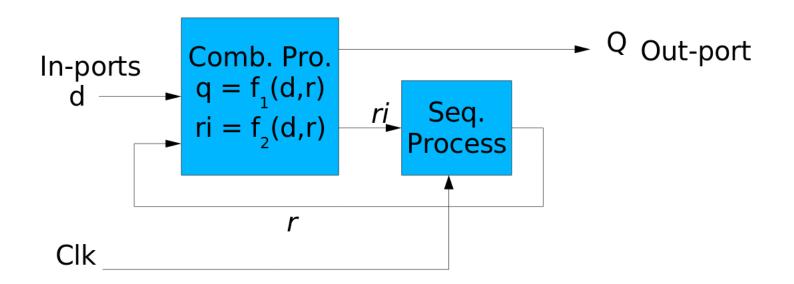

- Gaisler two-process implementations (www.gaisler.com/doc/structdesign.pdf)

- Combinational

with a few record output signals, one of which is total internal state

Clocked

generally only registers the above internal state, and handles reset

- Small number of processes

- Few signals, mostly in/out/state records

- Variables

- Functions / procedures

• From "A Structured VHDL Design Method" by Jiri Gaisler.

### **Two-process VHDL entity**

- Algorithms easily extracted

- Easy to extend

- Readability = Maintainability

- Fast simulation

- Easier debugging and verification

- No simulation/synthesis discrepancies

- Example: Current NOEL-V integer pipeline

- 2 processes

- Combinational, 2200 lines

- Clocked, 60 lines

- 53/22 procedures/functions, ~5000 lines (not counting generic ones from other files)

- 17 in port signals

- 13 out port signals

- 4 local signals (+12 for disassembler)

- The in/out ports connect to separate modules for: caches, register file, branch prediction, IRQ, debug, mul/div.

- **Example:** Current NOEL-V cache controller and MMU

- 3 processes

- Combinational, 3500 lines

- Two clocked, one assignment each (+debug)

- 10/45 procedures/functions, ~1500 lines (not counting generic ones from other files)

- 12 in port signals

- 4 out port signals

- 4 local signals (+2 for debug)

- The in/out ports connect to: AHB bus, caches, integer pipeline.

- Both LEON5 (Sparc) and NOEL-V (RISC-V)!

### • **Example:** First half of the execute stage.

```

ex flush := '0';

if wb_fence_i = '1' or v.wb.flushall = '1' or x_branch = '1' then

ex_flush := '1';

end if;

ex branch flush := '0';

if wb_fence_i = '1' or v.wb.flushall = '1' then

ex branch flush := '1';

end if;

ex forwarding(...); -- Lane 0

ex_forwarding(...); -- Lane 1

branch_unit(...);

jump_ex_forwarding(...);

jump_unit(...);

alu execute(...);

-- ALU0

-- ALU1

alu_execute(...);

ex_stdata_forwarding(...);

mul_gen(...);

for i in 0 to ISSUEWAYS-1 loop

:= r.e.ctrl(i).xc;

ex_xc(i)

ex_xc_cause(i)

:= r.e.ctrl(i).cause;

ex_xc_tval(i)

:= r.e.ctrl(i).tval;

end loop;

```

•••

### • **Example:** Detail from the execute stage.

```

-- Forwarding Lane 1 -----

ex_forwarding(r,

-- in : Registers

-- in : Lane 1

1,

r.e.forw(1),

-- in : Forwarded from Memory

-- out : Output op1 from Mux

ex_alu_op1(1),

-- out : Output op2 from Mux

ex_alu_op2(1)

);

-- Branch Unit -----

branch unit(ex alu op1(1),

-- in : Forwarded Op1

-- in : Forwarded Op2

ex_alu_op2(1),

r.e.ctrl(1).valid,

-- in : Enable/Valid Signal

r.e.ctrl(1).branch.valid,

-- in : Branch Valid Signal

r.e.ctrl(1).inst(14 downto 12),

-- in : Inst funct3

-- in : Branch Target Address

r.e.ctrl(1).branch.addr,

r.e.ctrl(1).branch.naddr,

-- in : Branch Next Address

r.e.ctrl(1).branch.taken,

-- in : Prediction

-- in : PC In

r.e.ctrl(1).pc,

ex branch valid,

-- out : Branch Valid

ex branch mis,

-- out : Branch Outcome

ex branch addr,

-- out : Branch Address

ex_branch_xc,

-- out : Branch Exception

-- out : Exception Cause

ex branch cause,

ex branch tval

-- out : Exception Value

);

```

```

www.Cobham.com/Gaisler

```

### • **Example:** Extract from the MMU/cache controller.

```

entity mmu_cache5v2rv is

generic (...);

port (

: in std ulogic;

rst

clk

: in std ulogic;

ici

: in icache_in_type4;

-- I$ requests from iu5

: out icache_out_type4;

-- replies

ico

: in dcache_in_type4;

-- D$ requests from iu5

dci

: out dcache out type4;

dco

-- replies

ahbi

: in ahb_mst_in_type;

-- AHB replies

: out ahb_mst_out_type;

ahbo

-- requests

: in ahb_slv_in_type;

-- AHB snoop address

ahbsi

ahbso

: in ahb_slv_out_vector;

-- AHB config data

crami

: out cram in type4;

-- tags and data to cache

: in cram out type4;

-- tags and data from cache

cramo

-- MMU and PMP configuration

: in csrtype;

csr

: in std_ulogic;

-- sclk for snoop (not gated)

sclk

);

end;

comb: process(r, rs, rst, ici, dci, ahbi, ahbsi, ahbso, cramo, csr)

reqs: process(clk)

sreqs: process(sclk)

...

```

## Verification

### NOEL-V Verification – how?

- Internally developed SystemVerilog framework

- Self-checking tests

- Match against golden model (spike)

- Instruction by instruction (some special handling, especially regarding time)

- Regression tests script

- Mainly Modelsim

- Mixed language

- Snap-shot for faster simulation

### NOEL-V Verification – what?

- Publicly available test suites, such as

- riscv-compliance

- riscv-dv

\_ riscv-torture

riscy-tests

- Internal random generator

- OS kernels

- Zephyr

- Rvirt

- RISC-V Proxy Kernel

- Linux

- RTEMS

- Applications

- Coverage

- Targeted tests

# Pipeline

### **NOEL-V** Integer pipeline

### **NOEL-V Fetch stage**

- Branch target buffer

- Branch history table

- Bimodal

- Two-level dynamic

#### www.Cobham.com/Gaisler

### NOEL-V Decode stage

- Expands compressed instructions

- Checks for dual-issue conflicts

- One unit: Memory, branch, mul/div, CSR

- CSR write first

- A few more, but late ALU helps

- Swap instructions if needed

- Memory in 0

- Branch in 1

- Check for illegal or privileged instruction

- Check for RAS hit and early branch

- Read register file and CSR

- RF is 4R/2W

- Generate ALU and instruction control

- Decide on early/late ALU/BU

- Pipeline bubbles only here

- Dependence on late ALU

- Non-committed CSR write to read CSR

- Memory access following MMU/PMP CSR write

- ...

### **NOEL-V Execution stage**

- Two equal ALUs

- Branch unit

- Combinational virtual address to data cache interface

- FPU and mul/div start here

# **NOEL-V Memory stage**

- Align data from cache

- Check TLB

- Check tags

- Virtually indexed, physically tagged

- L1 write-through, blocking

- Separate instruction and data caches

- Up to 4-way associative, LRU

- FSM to deal with cache/TLB miss, store buffer full

- Hardware page table walk

- Snooping for coherence

- Full PMP support, configurable

## **NOEL-V Exception stage**

- Two more full ALUs

- Another branch unit

- Write to CSR

- Collect exceptions

- External interrupts

## **NOEL-V** Write-back stage

- Write to register file

- Update branch prediction and RAS.

## NOEL-V Current pipeline in use

```

uintptr_t a[LENGTH], b[LENGTH], c[LENGTH];

```

```

...

for(int i = 0; i < LENGTH; i++) {

a[i] = b[i] + c[i];

}

```

loop:

```

Ida1, 0(a2)addia2, a2, 8Ida4, 0(a5)addia3, a3, 8addia5, a5, 8adda4, a4, a1sda4, -8(a3)bnea5, a0, loop

```

Pairing when first instruction is not 8-byte aligned.

loop:

| ld           | a1, 0(a2)                |                                         |

|--------------|--------------------------|-----------------------------------------|

| addi<br>Id   | a2, a2, 8<br>a4, 0(a5)   | swapped<br>since this must be in lane 0 |

| addi<br>addi | a3, a3, 8<br>a5, a5, 8   |                                         |

| add<br>sd    | a4, a4, a1<br>a4, -8(a3) | swapped<br>since this must be in lane 0 |

| bne          | a5, a0, loop             |                                         |

8 instructions in 5 cycles!

#### Pairing when first instruction is 8-byte aligned.

loop:

| ld<br>addi  | a1, 0(a2)<br>a2, a2, 8     |          |

|-------------|----------------------------|----------|

| ld<br>addi  | a4, 0(a5)<br>a3, a3, 8     |          |

| addi<br>add | a5, a5, 8<br>a4, a4, a1    | late ALU |

| sd<br>bne   | a4, -8(a3)<br>a5, a0, loop | wait     |

8 instructions in 7 cycles.

#### Different code generation, also 8-byte aligned.

loop:

| ld                  | a4, 0(a5)                                     | swapped, paired with branch at end |

|---------------------|-----------------------------------------------|------------------------------------|

| ld<br>addi          | a1, 0(a2)<br>a5, a5, 8                        |                                    |

| addi<br>add         | a2, a2, 8<br>a4, a4, a1                       | late ALU                           |

| sd<br>addi          | a4, 0(a3)<br>a3, a3, 8                        | wait                               |

| bne<br>Id<br>Again, | a5, a0, loop<br>a4, 0(a5)<br>8 instructions i | n 7 cycles.                        |

# Thanks for listening!

# COBHAM

# Shameless plug: Looking for talent!

https://www.gaisler.com/career

# COBHAM

#### COBHAM