# ControlPULP: A Multi-Core RISC-V Power Controller for HPC Processors

Alessandro Ottaviano<sup>1</sup>, Robert Balas<sup>1</sup>, Giovanni Bambini<sup>2</sup>, Davide Rossi<sup>2</sup>, Luca Benini<sup>1,2</sup>, Andrea Bartolini<sup>2</sup>

<sup>1</sup>IIS, ETH Zurich; <sup>2</sup>DEI, University Of Bologna;

1 Why an integrated multi-core Power Controller? 4 Evaluation

- Integrated Power Controller Systems (PCS) are key elements for governing the power consumption of modern HPC servers<sup>1</sup>.

- RISC-V lacks a reference design to conduct on-chip power management.

- More scalable and flexible PCS architectures are required to support advanced MIMO control algorithms and track PVT variability than single-core SoA solutions<sup>2</sup>.

#### 2 The ControlPULP platform

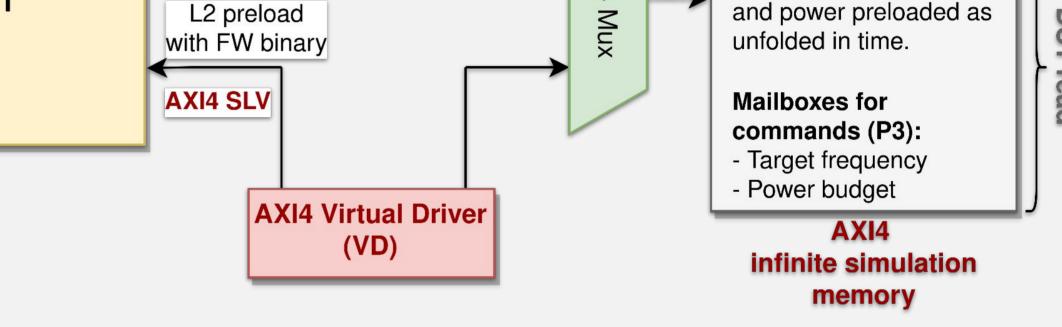

RTL Cycle-accurate simulation framework.

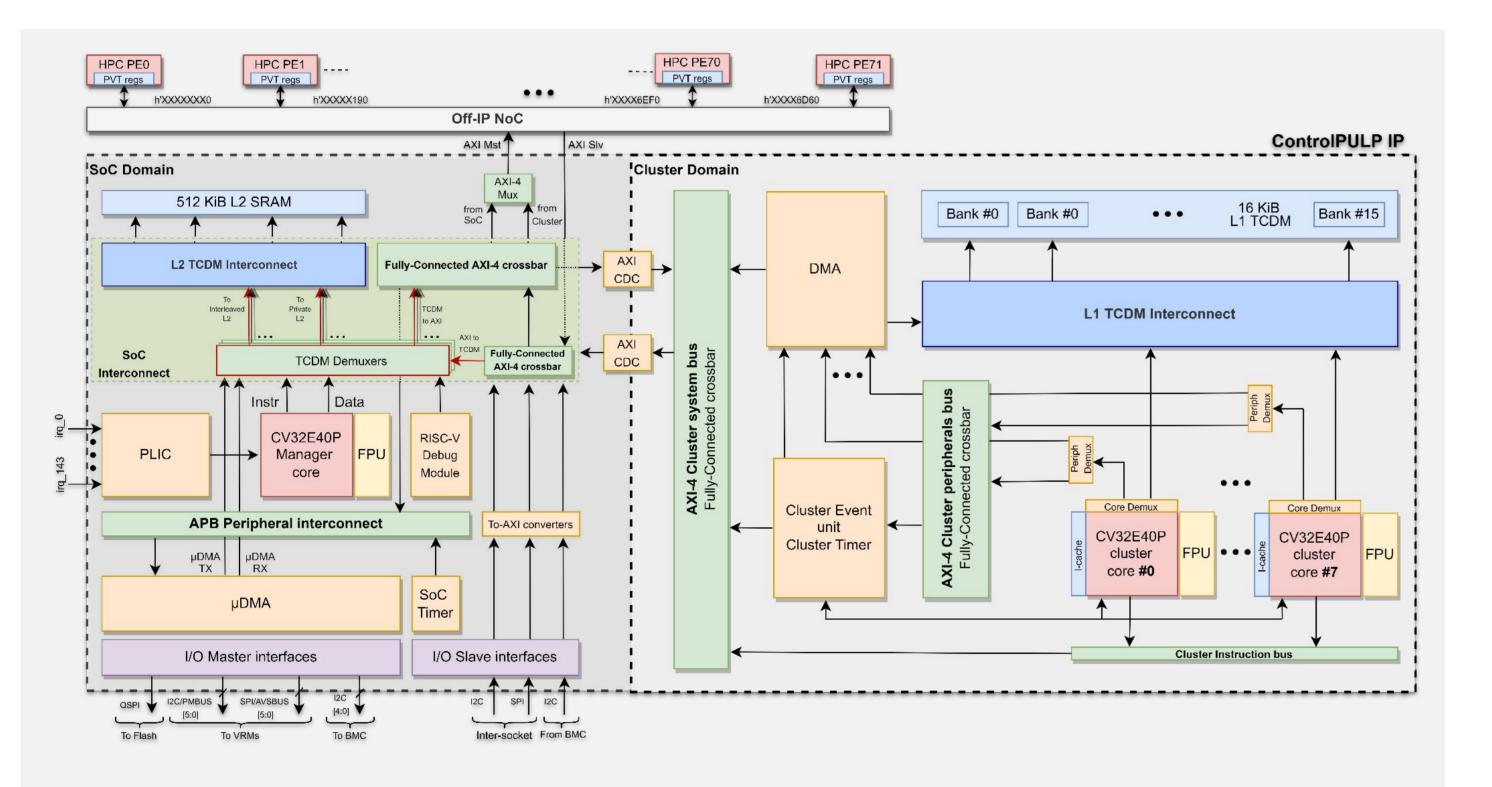

- Scalable architecture: multi-core cluster with private FPUs, DMA for PVT sensor data acquisition, low-latency PLIC interrupt controller.

- Power management interface: AVSBUS/PMBUS for off-chip VRMs interaction, ARM SCMI for on-chip OS interaction.

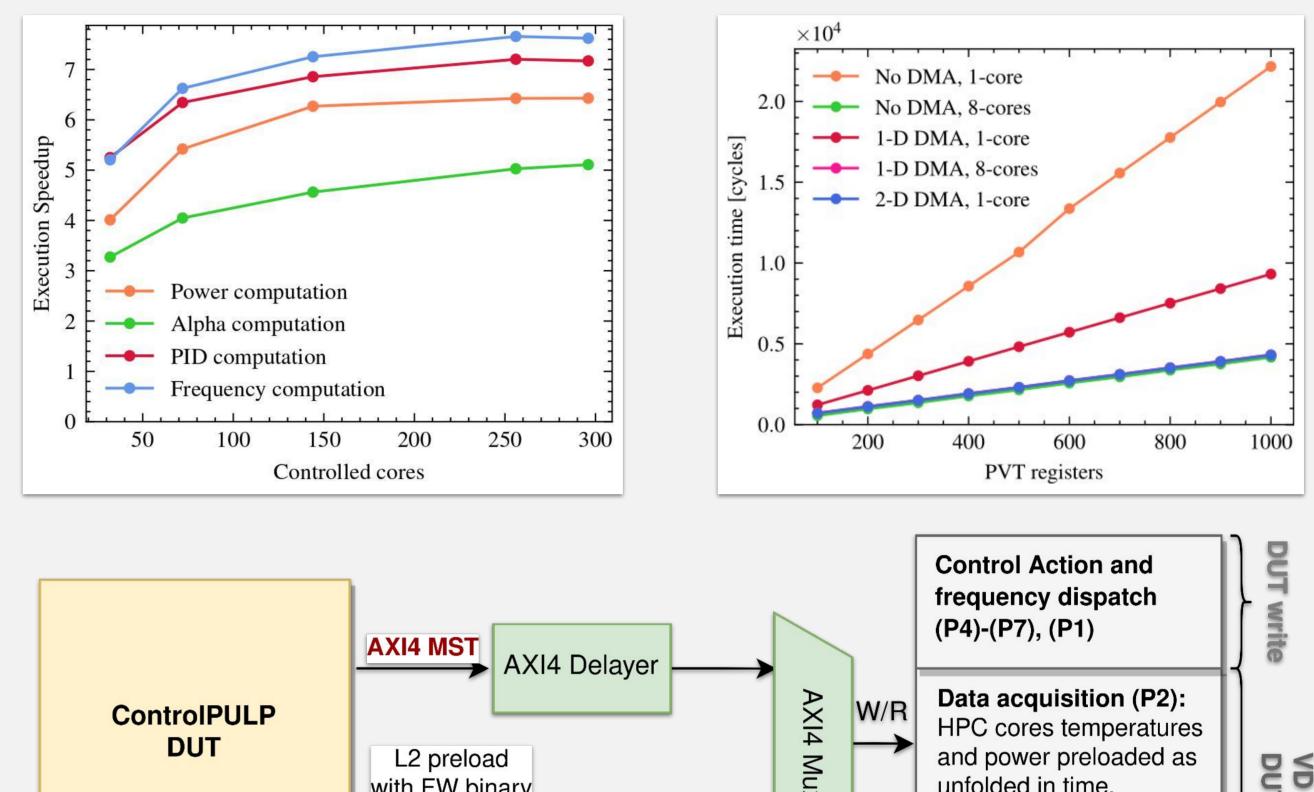

- PCF acceleration leads to overall 4.9x speedup with multi-core cluster execution and 2-D DMA-based PVT registers data acquisition against single-core, non-DMA based execution.

## 5 Conclusion

The first fully open-source (HW/SW) RISC-V parallel PCS with configurable number of cores and interfaces.

Designed to track the computational requirements of current and future HPC processors.

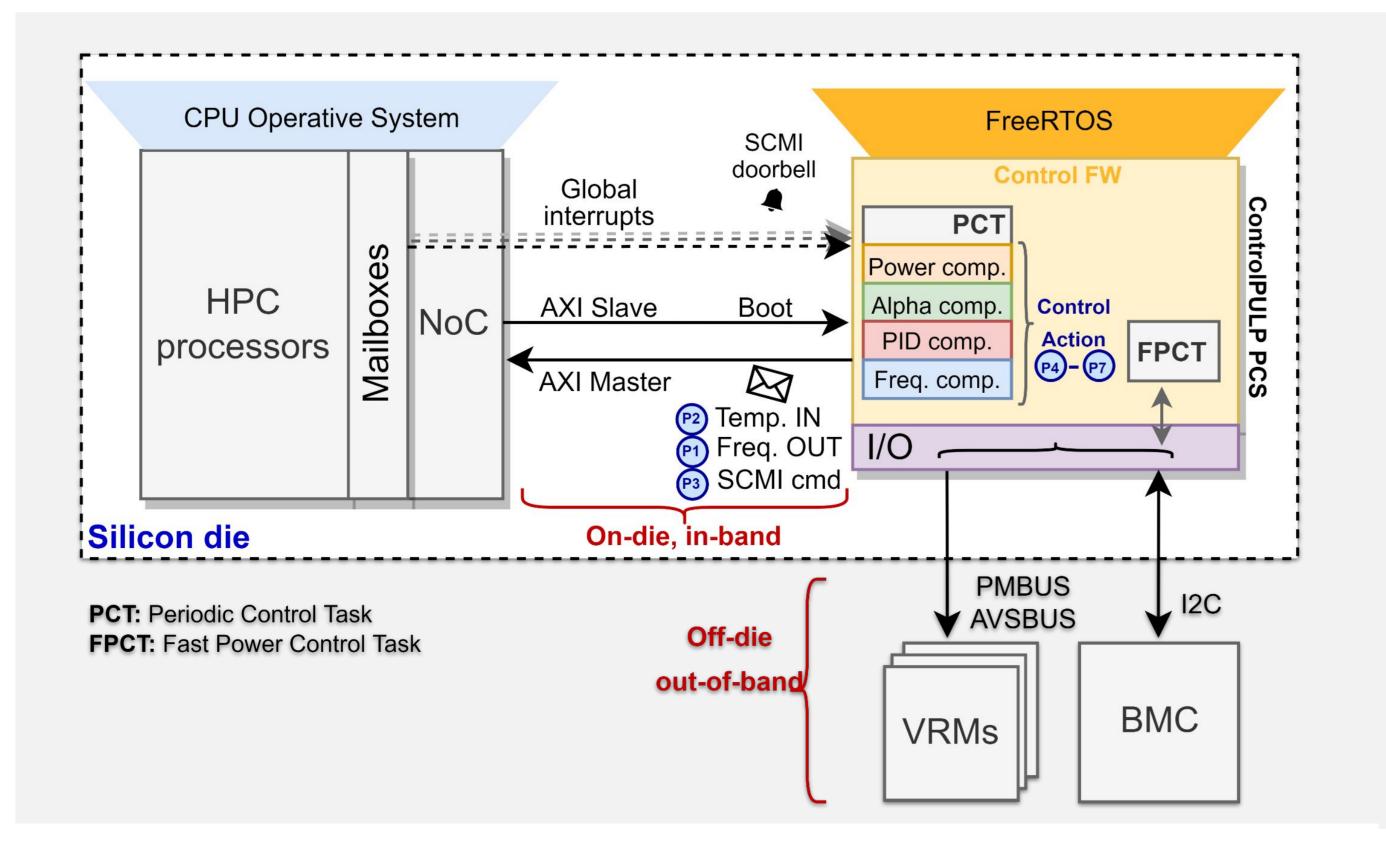

### 3 The Power Control Firmware

- Per-core power regulation.

- Relies on industry-grade Real-Time OS, FreeRTOS.

- Periodic Control Task (PCT, 2 kHz) and Fast Power Control Task (FPCT, 8 kHz) tackle OS and BMC operating point and power budget requests respectively.

- Compares favorably with SoA and open standard FW, IBM OCC (6% more precise setpoint tracking on heavy workloads).

[1] G. Bambini et al., "An Open-Source Scalable Thermal and Power Controller for HPC Processors," 2020.

[2] R. Schöne, T. Ilsche, M. Bielert, A. Gocht and D. Hackenberg, "Energy Efficiency Features of the Intel Skylake-SP Processor and Their Impact on Perform

[2] R. Schöne, T. Ilsche, M. Bielert, A. Gocht and D. Hackenberg, "Energy Efficiency Features of the Intel Skylake-SP Processor and Their Impact on Performance," 2019.