# SiFive The Inventors of RISC-V

May 2022

# SiFive - The Founder and Leader in RISC-V Computing

300+

design wins

100+

companies

8<sub>of</sub>10

top semiconductor companies work with us

## **Si**Five

## Leading the RISC-V revolution

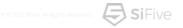

## We invented RISC-V

SiFive's founders are the same UC Berkeley professor and PhDs who invented and have been leading the commercialization of the RISC-V Instruction Set Architecture (ISA) since 2010

©2022 SiFive

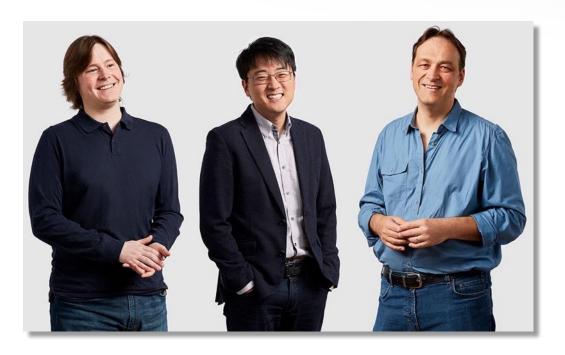

## SiFive global presence

#### **Presence**

- 10+ Offices

- 500+ Employees (420+ Engineers)

### **World Leading R&D**

- Inventors of RISC-V

- 100+ PhDs

- Highly experienced Processor team (e.g., Arm, Apple, AMD)

Backed by the World's Most Innovative VCs, Silicon Companies

## Undisputed leader in RISC-V computing

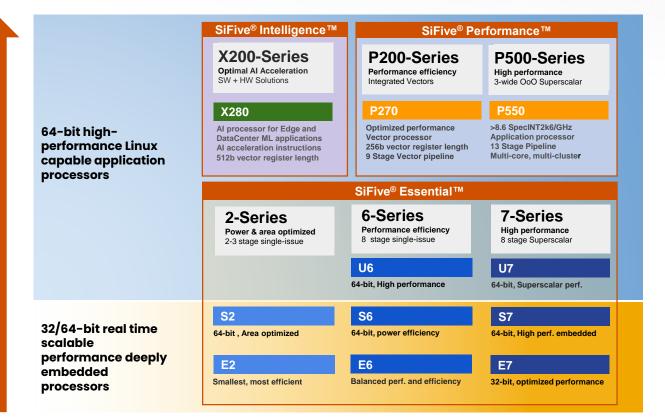

Complete portfolio of processors from embedded to high-performance computing

#### **CPU Cores**

SiFive Essential™

#### 32 and 64-bit Processors

- Microcontrollers, IoT devices, real-time control, control plane processing

- Highly customizable to application specific requirements

- Mature, industry proven designs

SiFive Performance™

#### **64-bit Application Processors**

- Networking, Infrastructure, Enterprise,

Consumer

- Highest performance, most advanced

RISC-V Processor available

- Scale out, high performance, processing capabilities with vector compute

#### Al Cores

SiFive Intelligence™

#### **Scalable Al Processors**

- Edge AI, Cloud, Training, Inference

- Very high performance and efficiency for AI workloads (vector processing)

- Built on top of RISC-V Vectors and the SiFive Intelligence Extensions

©2022 SiFive 5

# SiFive RISC-V processor IP portfolio

**High Performance**

**Broadest Portfolio**

**Relentless Innovation**

©2022 SiFive

# The future of RISC-V has no limits