Calista Redmond CEO, RISC-V International

May 2022

# Open source and collaboration are strategic to software and hardware across industries and geographies.

# This is our time. RISC-V empowers our community to seize growing opportunities

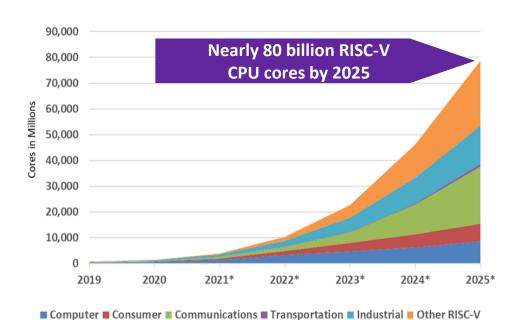

#### RISC-V CPU core market grows 114.9% CAGR, capturing >14% of all CPU cores by 2025

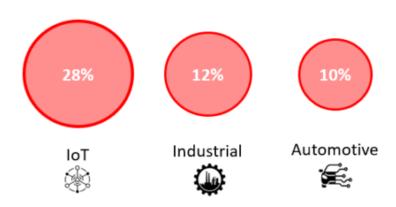

#### RISC-V Penetration Rate by 2025

"The rise of RISC-V cannot be ignored... RISC-V will shake up the \$8.6 Billion semiconductor IP market."

-- William Li, Counterpoint Research

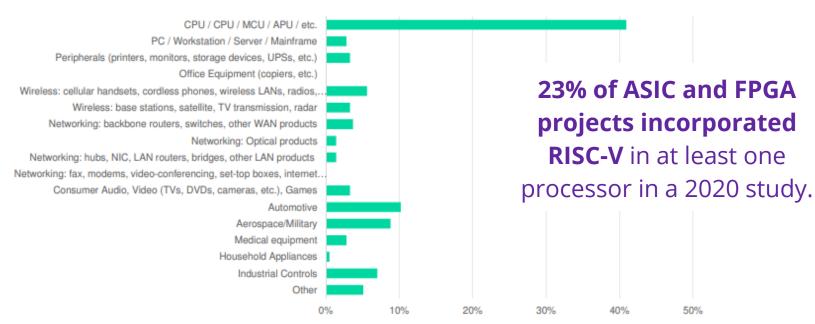

### Nearly a quarter of designs incorporate RISC-V

#### **Projects Incorporating RISC-V by Market Segment**

# RISC-V is the free and open Instruction Set Architecture

- ... Simple, modular architecture

- ... Open collaboration

- ... Design freedom

- ... Strategic future

### Disruptive **Technology** .

**Barriers**

**Proprietary**

**RISC-V**

Complexity

1500+ base instructions Incremental ISA

**Simple.** 47 base instructions, Modular ISA

Design freedom

Complex and limited, deep investment

Complete freedom.

Flexible, open building blocks

#### **Barriers**

License fees, Cost of entry

Design cost + constraint

Strategic risk

#### **Proprietary**

\$\$\$

\$\$\$ - Limited

Vendor lock in and dependency

#### **RISC-V**

Free

Free - Unlimited

Global community.

Invested stakeholders, No vendor lock in

**Unconstrained Opportunity**

# 2 billion RISC-V cores in market in 2021

"Deloitte Global predicts that

the market for RISC-V processing cores will double in 2022 from what it was in 2021, and that it will double again in 2023,

as the served addressable market available for RISC-V processing cores continues to expand."

industry adoption

#### Investment and traction accelerate in 2022

#### intel

**Intel Corporation Makes** Deep Investment in RISC-V Community to Accelerate **Innovation in Open** Computing

RISC-V welcomes Intel to the Board of Directors to collaborate on RISC-V IP

Intel Creates \$1B Innovation Fund To Grow RISC-V Market (And Attract New Foundry Customers) | Karl Freund, Forbes

February 7, 2022

Andes Technology Announces over 10 Billion Cumulative Shipments of Andes-Embedded SoCs and Records All-Time High Annual and Monthly Revenue in 2021

March 8, 2022

We're thrilled to be featured on the @Nasdag video wall this morning to celebrate our historic moment: a \$2.5B valuation from our Series F round! #RISCV #Nol imits

10:02 am · 16 Mar 2022 · HubSpot

Revised 2021 estimate 12 billion RISC-V cores

Europe invests early as a global open source citizen

EPAC embraced open-source philosophy of give and take, contributing to the RISC-V ecosystem and adding to LLVM compiler database, Linux OS and HPC software such as OpenMP and MPI. Hardware like STX were developed using the PULP platform

- HIPEACINFO 65

The European Commission <u>announced a new European Chips Act of €15 billion in additional public and private investments until 2030</u>. This adds to €30 billion of public investments previously earmarked.

— Tue, Feb 8 2022

Intel to spend €17bn on chip mega-factory in Germany... expands

manufacturing in Ireland, plus R&D and packaging across Europe — Tue 15 Mar 2022

- **Esperanto** 1,000-Core RISC-V Al accelerator.

- Alibaba RISC-V Xuantie processors with 4 open source cloud and edge processors

- Imagination RISC-V CPU family, for discrete and heterogeneous computing

- Seagate hard disk drive controller with high-performance RISC-V CPU.

- Ventana performance chiplet approach to data center SoC design

- Intel Nios processor based on RISC-V, designed for performance.

RISC-V CPU core market will grow 115% CAGR, capturing >14% of all CPU cores by 2025

#### Communication Al SoC RISC-V designs will grow 21.2% CAGR from 2019-27 - Semico Research, December 2021

- **Andes** RISC-V processor adopted by SK Telecom for AI products.

- **Alibaba** supporting Android 12 on their 64-bit RISC-V core emulated in QEMU

- **Sipeed** RISC-V chip runs Android 10, RV64 phone coming next

- Alibaba ported TensorFlow Lite for Al image, audio, and optical in smart devices.

- **Google** Pixel 6 Titan M2 RISC-V processor, with extra speed and memory, more resilient to advanced attacks.

- MobileEye vision-based advanced driver assist systems chips capable of 176 trillion ops per second with 12 RISC-V CPU cores.

- Andes ISO 26262 Functional Safety ASIL D Dev Process Certification for RISC-V embedded automotive safety with Andes processors

- Imagination Technologies GPU linked by a RISC-V core for ASIL-B level designs with ISO 26262 safety critical certification.

- IAR Systems extended functional safety of its Embedded Workbench sw tool chain to the RISC-V core of NSITEXE, subsidiary of automotive leader Denso.

- Europe GaNext simplifies power converters with GaN power semiconductors with better efficiency and compactness for EV chargers.

2020 RISC-V automotive opportunity 4M cores; growing to 150M cores in 2022 and 2.9B cores by 2025.

- Deloitte, December 2021

RISC-V will capture 10% of the Automotive market by 2025

- Huawei Hi3861 RISC-V board for Harmony OS developers for IoT

- Zepp Health / Huami wearable manufacturer OS supporting RISC-V Reference Models for RISC-V P extension

- GreenWaves ultra-low power GAP9

hearables platform for scene-aware and

neural network-based noise reduction.

- RIOS Lab announced PicoRio, an affordable RISC-V open source smallboard computer.

- SiFive world's fastest development board for RISC-V Personal Computers.

RISC-V will command 28% of the IoT market by 2025

- Counterpoint Technology Market Research, September 2021

### RISC-V-based AI SoCs will grow 73.6% CAGR to 25B units and

**\$291B** in revenue by 2027

Alibaba Cloud tops MLPerf Tiny v0.7

Benchmark with its IOT processor

- StarFive released the world's first RISC-V AI visual processing platform

- Andes released superscalar multicore and L2 cache controller processors.

- NVIDIA CUDA support on Vortex RISC-V GPGPU enables scaling from 1-core to 32core GPU based on RV32IMF ISA with OpenCL 1.2 graphics API support.

- Fraunhofer ported Tensorflow lite to their RISC-V processor core for Edge Al applications incl sensor data evaluation, gesture control, or vibration analysis.

- Seeed Studio's new Sipeed MAIX, a RISC-V 64 Al board for Edge Computing makes it possible to embed Al to any IoT device.

- Micro Magic announced an incredibly fast 64-bit RISC-V core achieving 5GHz and 13,000 CoreMarks at 1.1V.

- Western Digital SweRV Core enables spectrum of compute at the edge

- Microchip released the first SoC FPGA development kit based on the RISC-V ISA.

- E4 Monte Cimone Cluster along with DEI-UNIBO contributing to architecture, software, and integration.

- **European Processor Initiative** RISC-V accelerator with first chip Sep 2021

- Technical University of Munich (TUM)

quantum cryptography chip for quantum

computing security demands

- Tactical Computing Labs HPC-centric software test suite for GCC and LLVM

- Cortus is developing a high-performance RISC-V Out-of-Order processor core for the European eProcessor project.

- De-RISC HW-SW platform for multi-core

RISC-V SoC for safety critical aerospace

# High Performance Computing

Johanna Baehr of TUM heads a team that has hidden four hardware Trojans on this chip - malicious functions that are integrated directly into the circuits.

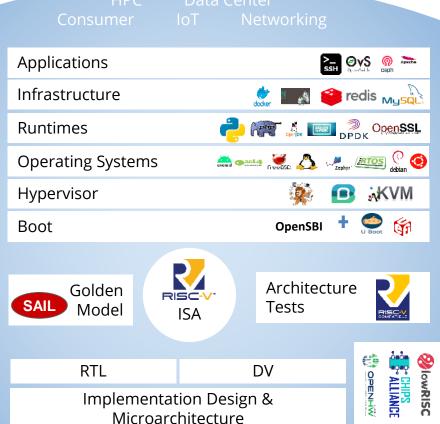

# Rich RISC-V Ecosystem Available Today

SAIL SPIKE 000 **% €**EMU Simulators Compilers CI/Testing Perf Tools

Services

Debuggable

Reliable,

Serviceable, Diagnosable

Performant

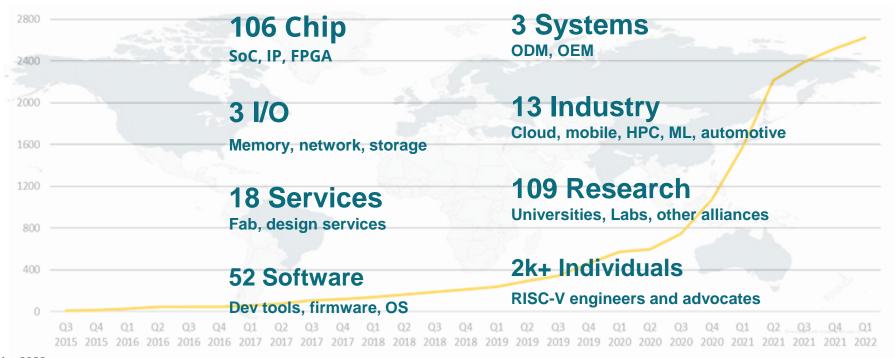

# More than 2,700 RISC-V Members across 70 Countries

groups

Guide strategic technical **Work**

Profiles & Platforms & Architecture Compatibility Tests (ACT) & Platform Compatibility Tests (PCT)

**Amplify** member news, content, and success with press and analysts

**Original** content programs RISC-V, industry, and regional **events**

Jobs and internships

Technical developer forums

# RISC-V delivers incredible member support

| Test Chips Software tests                 | managementa |                                                                                                                                                                                      |                                                      | Al SoCs, Application processors, Linux Drivers, Al Compilers SIGS: Security Response, Al, Graphics, Android, Embedded, Datacenter/Cloud, Blockchain, Simulators, Managed Runtimes, Android, Functional Safety  Programs: Dev Board Seed, Development | SIGS: Vector, Perf Modeling, Perf Analysis, Trusted Computing, Control Flow Integrity, Memory Protection, Microarchitecture Side Channel, QOS, E2E Data Integrity, Error Handling, Automotive, Communications, Floating Point, Vector Security specs; RISC-V Security Model, AP-TEE, IOPMP Platform specs: Platforms, SEE, SBI, ABI, Discovery, Watchdog, ACPI, UEFI |                                |

|-------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Linux port                                | software    | partnership                                                                                                                                                                          |                                                      | Partners, RISC-V Labs                                                                                                                                                                                                                                | <b>SOC specs</b> : E-Trace, Nexus, IOMM                                                                                                                                                                                                                                                                                                                              | U Ecosystem                    |

| 2010-2016                                 | 2018        | 2019                                                                                                                                                                                 | 2020                                                 | 2021                                                                                                                                                                                                                                                 | 2022                                                                                                                                                                                                                                                                                                                                                                 | 2023 →                         |

| ISA<br>Definition<br>RISC-V<br>Foundation | RV32        | RV32I and RV64I Base instructions: Integer, float,double, quad, atomic, and compressed instructions Priv modes, Interrupts, exceptions, memory model, protection, and virtual memory | Architecture<br>Compatibilit<br>y Framework<br>Trace | Vector Crypto Scalar Bitmanip Hypervisor ePMP Cache Mgt Virtual Memory Zfh Zfinx Zihintpause                                                                                                                                                         | Profiles Packed SIMD Advanced Interrupts Java: ptr masking, I/D synch RV32E & RV64E Bfloat16 Vector Half-Precision Floating Poin Code Size Crypto Vector Fast Interrupts SMPU Zmmul                                                                                                                                                                                  | Matrix Ops<br>Crypto Gost<br>t |

| RISC-V°                                   |             |                                                                                                                                                                                      |                                                      |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                      | ISA Extensions                 |

# Investments in open source bring a 4x return

**EU companies invested €1 billion** in Open Source Software in 2018, providing economic impact of €65 - €95 billion, with a cost-benefit ratio of >1:4.

### **Technical advantage**

**Lower maintenance costs.** Contributing to upstream projects ensures technical elements will be included in future updates without ongoing development costs.

**Influence direction.** New features come from contributions. To include functionality important to your organization, you need to support active project contributors.

#### **Talent matters**

**Open source saves time and money.** Developers can save ~45 minutes a day with open source. For an organisation of 1,800 people, this can be financial savings of \$12.4 million over three years.

**Attract, retain, and build technical talent and collaborative culture.** 48% of businesses contributed to open source projects to access developer talent. Employees relationships and identify good fits for your company while working on their favorite project.

As one Global, connected movement

@risc\_v @calista\_redmond

risc-v-international calistaredmond

# Benefits of engaging in RISC-V

- ✓ Accelerate technical traction and insight

- ✓ Contribute technical priorities, approaches, and code

- ✓ Gain strategic and technical advantage

- ✓ Increase visibility, leadership, and market insight

- ✓ Fill and increase engineering skills, retain and attract talent

- ✓ Build innovation partner network and customer pipeline

- ✓ Deepen, engage, and lead in local and industry developer network

- ✓ Showcase RISC-V products, services, training, and resources

# Membership Options

#### **Premier Member Benefits**

- Board seat and Technical Steering Committee seat included at \$250k level

- Technical Steering Committee seat included at \$100k level

- Board level includes seat on RISC-V Legal Committee

- Eligible to lead workgroup and/or committee

- Use of RISC-V Trademark for commercialization

- Member logo / name listing on RISC-V website, alphabetical with Premier members

- Solution / Product listing highlighted on RISC-V Exchange, noted with member level

- 4 case studies a year

- 2 blogs per month

- 2 social media spotlights per month

- Spotlight member profile

- Event sponsorship discount

#### **Premier Requirements**

- Membership open to any type of legal entity

- \$250k Annual membership fee that includes Board seat and TSC seat

- \$100k Annual membership fee that includes TSC seat

#### **Strategic Member Benefits**

- 3 Board reps elected for the Strategic tier, including Premier members that do not otherwise have a board seat

- Eligible to lead workgroup and/or committee

- Use of RISC-V Trademark for commercialization

- Member logo / name listing on RISC-V website, alphabetical with Strategic members

- Solution / Product listing highlighted on the RISC-V Exchange, noted with member level

- 1 case study a year

- 1 blog per month

- 1 social media spotlight per month

- Event sponsorship discount

#### **Community Member Benefits**

- Two Board representatives

- 1 Community Board representative, elected

- 1 Individual Board representative, elected

- Member logo / name listing on RISC-V website, by member level

- 1 case study a year

- 1 blog per quarter

- 1 social media spotlight per quarter

- Event sponsorship discount

#### **Strategic Member Requirements**

- Membership open to any type of legal entity

- · Annual membership fee based on employee size

- 5,000+ employees: \$35k

- 500-5,000 employees: \$15k

- <500 employees: \$5k</li>

- <10 employees & company <2 yrs old: \$2k</li>

#### **Community Requirements**

- Membership open to

- o academic institutions,

- non-profits,

- o individuals not representing a legal entity

- No annual membership fee

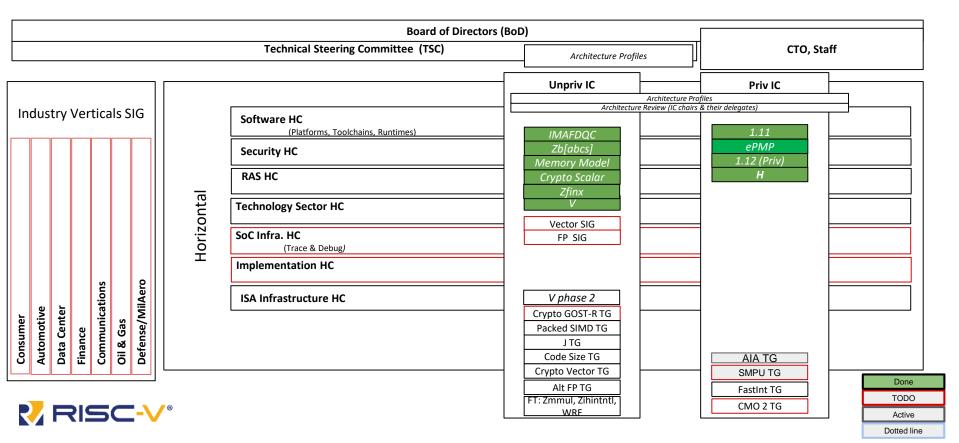

# Technical Organization

## Software Horizontal Committee

AI/ML/NLP/Graphics SIG

Android SIG

Perf Modeling SIG

Perf Analysis SIG

**IOMMU TG**

#### Platform HSC

Hypervisors SIG

AIA TG

Config TG

#### Topics TODO:

- Linux class OSs

- RTOSs

- DMA

- Multi-processing

- JITs

- IOMMU, Buses

- Bootloaders

- Distro coordination/build/rel

- QOS

- Perf monitoring

TGs for specs underway

IOPMP TG

OS-A Platform SIG

RVM-CSI Platform TG

OS-A SEE TG

OS-A PlatformTG

OS-A PCT TG

#### Toolchain & Runtimes HSC

psABI TG

#### Topics TODO:

- Benchmarks

- Regression test strategy

- Ecosystem changesExtensions needed

- Worst Case Execution Time

- (WCET)

Spatial & Timing interference

DSP

- DB & Hadoop et al.

- Performance analysis

- Native code

- ∘ GCC

- ∘ LLVM

- Optimizer

- Profileradb

Code Size TG

**HPC SIG**

Managed Runtimes SIG

SOC Infrastructure HC

Security HC

RAS HC

ISA Infrastructure HC

**Technology Sectors** HC

Data Center SIG

**HPC SIG**

Embedded SIG

Implementation Virtual HC

Final Cost/Benefit/ Completeness Checks by SW & Unpriv & Priv Committee chairs

Debug & Trace HSC

Crypto Vector TG Crypto GOST-R TG Functional Safety SIG QOS SIG

E2E Data Integrity SIG

Error recording, reporting,

isolation SIG

Documentation SIG

E-Trace Code

Debug revision TG

E-Trace Data TG

Nexus TG

IOMMU TG

IOPMP TG

MPU TG

Security Model TG Debug 0.1X

Security Response SIG

Blockchain SIG

Trusted Computing SIG

AP-TEE TG

Control Flow Integrity SIG

Microarchitecture Side Channel SIG

Memory Safety SIG

IOPMP TG

SMPU TG

TODO

- Diagnosability

- Recoverability

- Data poisoning containment

- PCIe error reporting

Fast Interrupts TG

Code Size TG

psABI TG

Packed SIMD TG

Debug TG

**TODO**

- Networking

- Wireless

- Edge

- Automotive Embedded

TODO

Strategy

- Platform Interrupts

- Power

Infrastructure

Management

RISC-V®

Done TODO Active

Dotted line

Strategy Architecture Tests Strategy

Formal Specification

Architecture Tests SIG

Simulators SIG

C/I Regression Tests SIG

# RISC-V Technical Programs

#### RISC-V Developer Boards

Available to spur innovation, provide hands-on education, and engage early adopters to test and develop.

### RISC-V Development Partner

Recognizes the investment and dedication of organizations making significant technical contributions to RISC-V.

#### **RISC-V Lab**

Institutions that host a lab with RISC-V hardware for CI/testing and general availability sandboxing.

#### **RISC-V Compatible**

Architectural Tests created to help ensure that software written will run on implementations that comply with that profile. Branding available for compatibility.

#### **RISC-V Platform**

A common, reusable runtime environment that operating systems and applications can target to improve portability and reuse. Provides interoperability assurance.

#### **RISC-V Profiles**

Refers to a base ISA and one or more extensions that are specified as a group so that applications can be compiled once, run on different implementations, and get the same results.

## Visibility Opportunities

RISC-V and Industry events

Local, regional, and global events

Speaking opportunities

Showcase and announce

RISC-V solutions

Networking

Host your own RISC-V Event

The RISC-V blog program showcases leadership, industry commentary, and technical information.

To submit content, fill out the Google Form or email content@riscv.org.

Share member and community news "In the News"

RISC-V provides quotes for member press releases Participate in media panels

and interviews

#### in Social

#### Twitter LinkedIn

Members submit original content for posting on RISC-V social channels

Members and the community submit content for re-sharing.

Amplify member announcements via social

To submit content, fill out the Google Form or email content@riscv.org.

Engage!

Promote member and community solutions

Connect developer community

#### **Case Studies**

Flevate technical conversations to business objectives and challenges, showing adoption of RISC-V.

Case studies on riscv.org are shared to media channels and analysts.

# Community and Learning

Alliances are Technical and strategic relationships across industries, geographies, and technical domains providing mutual community support

RISC-V Ambassadors are the technical experts and leaders in the RISC-V community.

They work together with RISC-V to help drive our global momentum and adoption of RISC-V technologies.

Meet the Ambassadors

#### ا <u>ل</u>ا

There are many materials to help you learn or teach RISC-V, including trainings, published books, technical and scholarly articles written around the world, and a lengthy collection of open educational materials provided by our community.

<u>University resources</u>

<u>Online Courses</u>

Training Partners

#### Talent

RISC-V paid Mentorships are offered quarterly with projects submitted by members and open applications to the community.

Looking for a job or want to post a RISC-V related job? Check our the <u>Careers</u> page!

#### **Open Hardware Diversity**

Alliance bringing together the open hardware community to support the professional advancement of underrepresented individuals in open source hardware.

Travel scholarships offered -for RISC-V Summit.

Engage!