A CPU is Only as Good as its Ecosystem:

# Turning RISC-V CPUs into Systems with FuseSoC

**Olof Kindgren**

Qamcom Research & Technology FOSSi Foundation Spring 2022 RISC-V week - Paris 2022.05.05

# Who am I?

Android crashes on boot when running from SD card

12:17 AM - 21 Mar 2017

Award-winning FOSSi Foundation COMPANY CONSIGNATION CONSIGNATI

RISCA

#### RISC-V SoftCPU Contest: Winners

• 1<sup>st</sup> Place: Charles Papon with VexRiscv - Awarded \$6,000 USD

2<sup>nd</sup> Place: Antti Lukats with Engine-V was

- Awarded \$3,000 USD, a Splash Kit and an iCE40 UltraPlus MDP

- 3<sup>rd</sup> Place: Changyi Gu with PulseRain Reindeer - Awarded \$1,000 USD, a PolarFire Evaluation Kit and an iCE40 UltraPlus Breakout Board

Creativity Prize: Olof Kindgren with SERV - Awarded \$3,000 USD

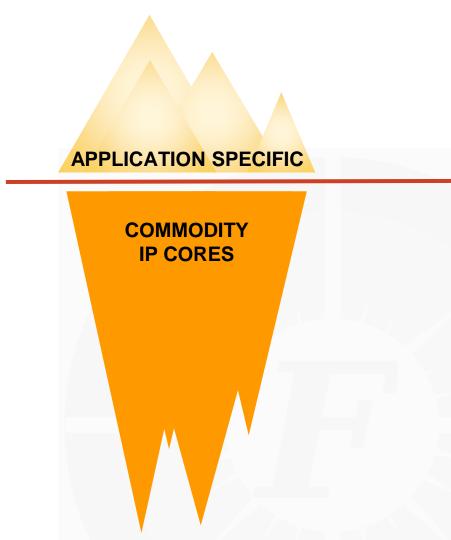

#### **IP** cores

Traditional HDL designs are built from IP cores.

Ideally, a product should be built upon a foundation of existing commodity IP cores with the value-add on top.

This is how software products are normally developed.

# **APPLICATION SPECIFIC COMMODITY IP CORES**

#### **IP** cores

IP cores come from four sources.

A non-trivial design normally use a mix of these.

- In-house developed

- 3rd party proprietary

- Platform-provided

- 3rd party open source

#### What is FuseSoc?

# What is FuseSoc?

FuseSoC is a package manager...

# What is FuseSoc?

FuseSoC is a package manager...

...and a build tool abstraction for HDL

It looks like you're making an IP core. Would you like help?

Get help with making the IP core

Just make the IP core without help

Don't show me this tip again

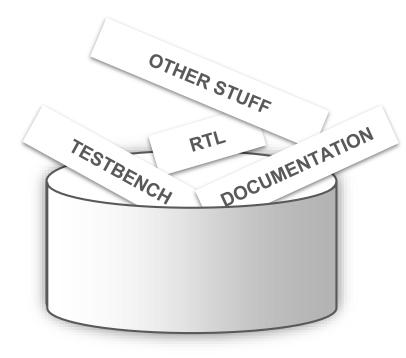

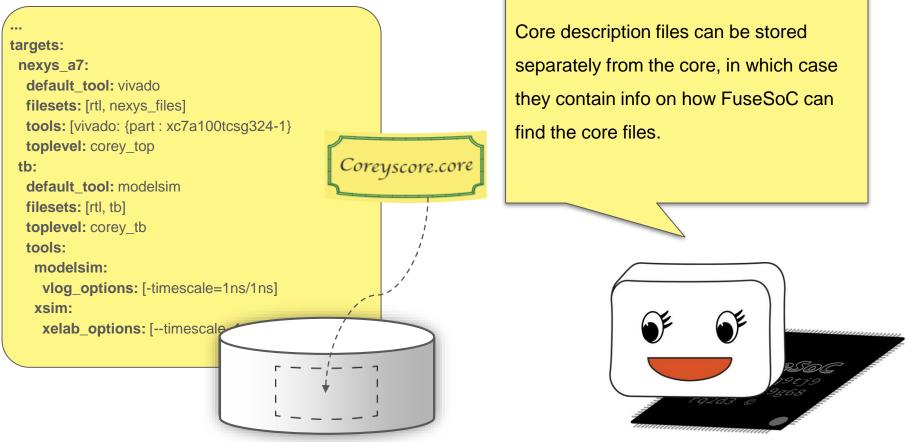

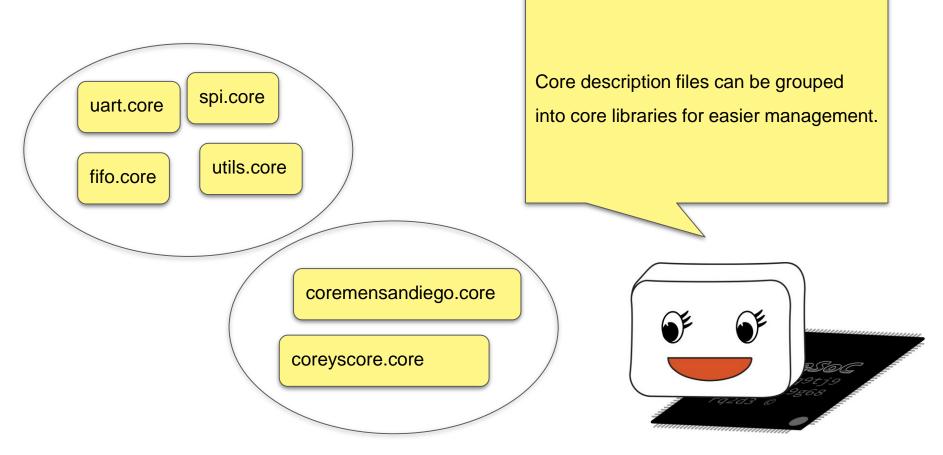

# **Core description files**

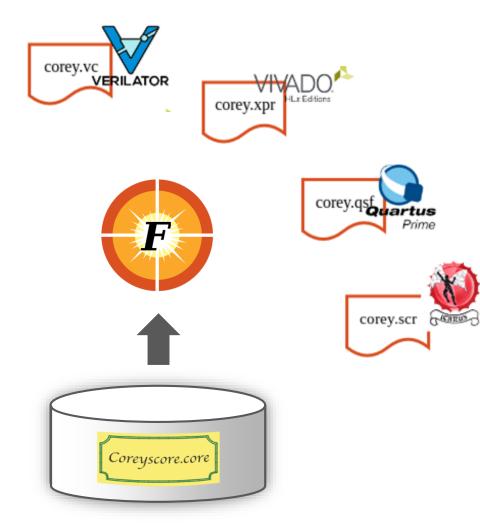

targets: nexys\_a7: default\_tool: vivado **filesets:** [rtl, nexys\_files] tools: [vivado: {part : xc7a100tcsg324-1} toplevel: corey\_top tb: default tool: modelsim filesets: [rtl, tb] toplevel: corey\_tb tools: modelsim: vlog\_options: [-timescale=1ns/1ns] xsim: xelab\_options: [--timescale Coreyscore.core

....

Core description files describe properties of the core that the EDA tools need e.g.

- files

- parameters

- tool options

# **Core description files**

.... targets: nexys\_a7: default tool: vivado filesets: [rtl, nexys\_files] **tools:** [vivado: {part : xc7a100tcsg324-1} toplevel: corey\_top tb: default tool: modelsim filesets: [rtl, tb] toplevel: corey\_tb tools: modelsim: vlog\_options: [-timescale=1ns/1ns] xsim: xelab\_options: [--timescale Coreyscore.core

Targets describes ways to use the core and its dependencies. Some targets, like a simulation target, can support several tools.

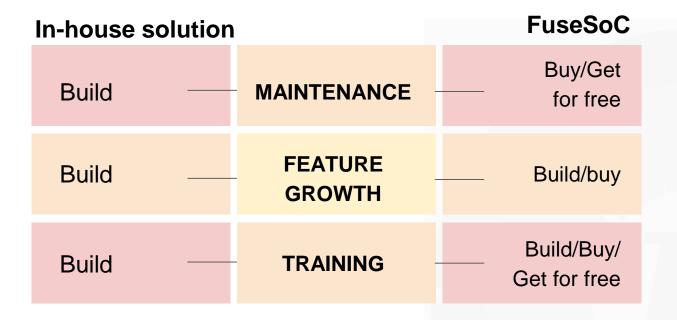

# Build or buy (or get for free)

# **Existing open source libraries**

| fusesoc-cores | 77  |

|---------------|-----|

| orpsoc-cores  | 100 |

| openpiton     | 66  |

| opentitan     | 129 |

| optimsoc      | 102 |

+ many smaller libraries e.g. CVA6, picorv32, PULP, serv, microwatt, SweRV

+ many proprietary libraries

Most prominent open source silicon projects already use or have started looking at using FuseSoC

#### Tomorrow

- Increased adoption

- Expanded base library

- Additional EDA tool support

- Public package pool (à la pypi)

#### Future

- Industry standard

- World-class documentation

#### Future

- Industry standard

- World class documcination

# Why use FuseSoc?

Increase reuse

Target different tools and devices with the same core description files

Share cores between different working groups

Reuse cores between projects

Reduce cost

Lower maintenance and on-boarding costs

Battle-proven base functionality that can be easily extended

Focus on your core business, not your cores.

https://github.com/olofk/serv https://github.com/olofk/observer https://github.com/olofk/corescore

https://www.linkedin.com/in/olofkindgren

Thank you for your time

https://twitter.com/OlofKindgren

**a**mcom

https://riscv.org/risc-v-ambassadors https://www.qamcom.com

https://github.com/olofk/fusesoc https://github.com/olofk/edalize

https://fossi-foundation.org https://chipsalliance.org

# Backup slides

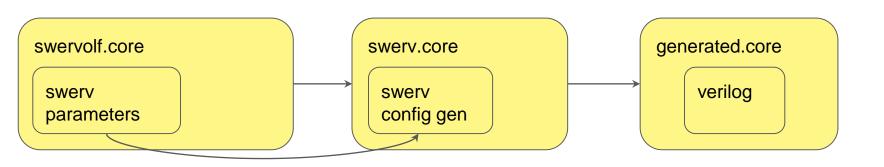

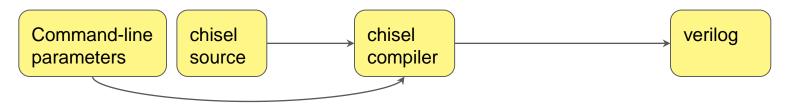

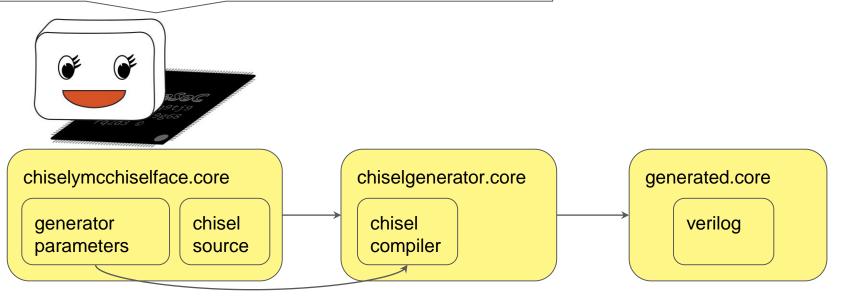

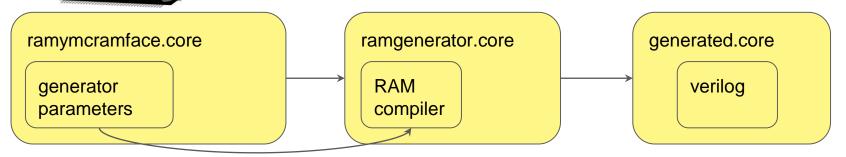

#### Core description files (generators)

EDA tools only speak (system)verilog (and VHDL). All other file types must be generated before being sent to the EDA tool

# Core description files (generators)

EDA tools only speak (system)verilog (and VHDL). All other file types must be generated before being sent to the EDA tool.

Generators can be shared between cores

#### oth Core description files (generators)

\$readmemh files **IP-XACT** toplevels => verilog => VHDL/SV packages/defines

CPU configuration

memory maps

С

generators

=>

=> interconnect

# Core description files (the other stuff)

Parameters

Tool-agnostic descriptions of `define, parameters, plusargs, generics... Controllable from command-line

Script hooks

Inject custom scripts before and after setup, build and run

VPI

Tool-agnostic way of compiling VPI libraries No DPI yet (but coming)

Probably more stuff I forgot

Ask me about FuseSoC

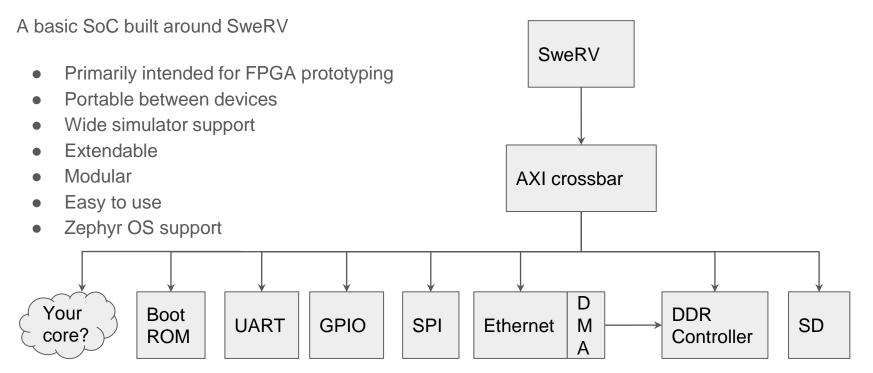

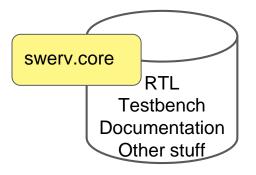

#### SweRV

# SweRVolf

#### SweRV

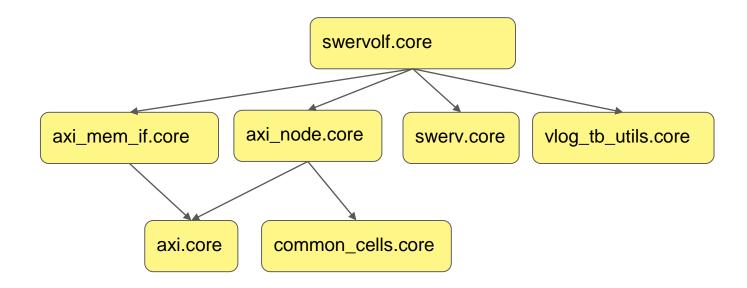

#### SweRVolf dependencies

#### Core description files (generators)